# Advanced Electronic Systems

Damien Prêle

#### ▶ To cite this version:

Damien Prêle. Advanced Electronic Systems . Master. Advanced Electronic Systems, Hanoi, Vietnam. 2017, pp.153. cel-00843641v6

## HAL Id: cel-00843641 https://cel.hal.science/cel-00843641v6

Submitted on 16 Nov 2017 (v6), last revised 12 Apr 2023 (v10)

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# advanced electronic systems ST 11.7 - Master SPACE

University of Science and Technology of Hanoi PARIS

Paris Diderot University DIDEROT

Lectures, tutorials and labs

2017-2018

## Contents

| I  | Fili   | ters                                                                          | 7  |

|----|--------|-------------------------------------------------------------------------------|----|

| 1  | Filte  | ers                                                                           | 9  |

|    | 1.1    | Introduction                                                                  | 9  |

|    | 1.2    | Filter parameters                                                             | 9  |

|    |        | 1.2.1 Voltage transfer function                                               | 9  |

|    |        | 1.2.2 S plane (Laplace domain)                                                | 11 |

|    |        | 1.2.3 Bode plot (Fourier domain)                                              | 12 |

|    | 1.3    | Cascading filter stages                                                       | 16 |

|    |        | 1.3.1 Polynomial equations                                                    | 17 |

|    |        | 1.3.2 Filter Tables                                                           | 20 |

|    |        | 1.3.3 The use of filter tables                                                | 22 |

|    |        | 1.3.4 Conversion from low-pass filter                                         | 23 |

|    | 1.4    | Filter synthesis                                                              | 25 |

|    |        | 1.4.1 Sallen-Key topology                                                     | 25 |

|    | 1.5    | Amplitude responses                                                           | 28 |

|    |        | 1.5.1 Filter specifications                                                   | 28 |

|    |        | 1.5.2 Amplitude response curves                                               | 29 |

|    | 1.6    | Switched capacitor filters                                                    | 33 |

|    |        | 1.6.1 Switched capacitor                                                      | 33 |

|    |        | 1.6.2 Switched capacitor filters                                              | 34 |

| Tu | ıtoria | al                                                                            | 37 |

| 10 | 1.7    |                                                                               | 37 |

|    | 1.8    | •                                                                             | 38 |

|    | 1.9    |                                                                               | 38 |

|    |        |                                                                               | 39 |

|    |        |                                                                               | 39 |

|    |        | . 7                                                                           | 39 |

|    |        | 9 .                                                                           | 39 |

|    | 1,10   | •                                                                             | 39 |

|    |        |                                                                               | 40 |

|    |        | 21201 <b>2</b> 101110 111 <b>0</b> 1101110 110110 110110 110110 110110 110110 |    |

| La |        |                                                                               | 41 |

|    |        |                                                                               | 41 |

|    |        | 1 ,                                                                           | 42 |

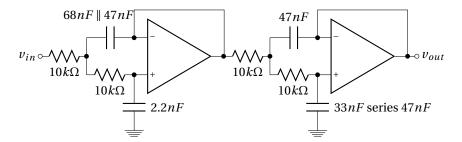

|    | 1.16   | Removing harmonics frequencies                                                | 43 |

| II | D        | DC Converters                               | <b>45</b> |

|----|----------|---------------------------------------------|-----------|

| 2  | DC/      | OC converters                               | 47        |

|    | 2.1      | Introduction                                | 47        |

|    |          | 2.1.1 Advantages/Disadvantages              | 47        |

|    |          | 2.1.2 Applications                          | 48        |

|    | 2.2      | DC/DC converters                            | 48        |

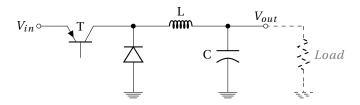

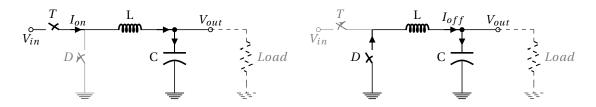

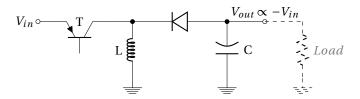

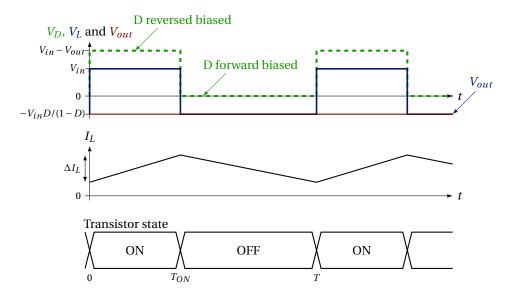

|    |          | 2.2.1 Buck converters                       | 49        |

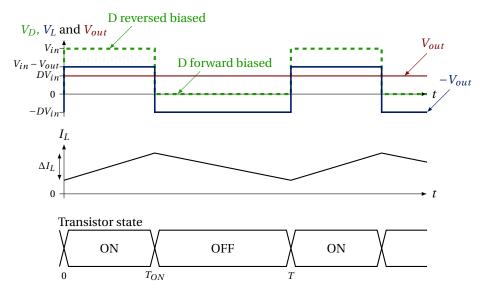

|    |          | 2.2.2 <i>Boost</i> converters               | 50        |

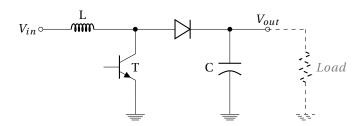

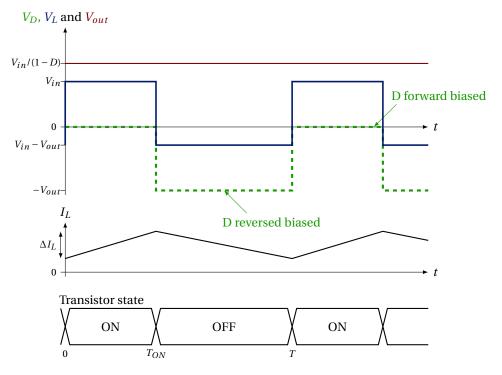

|    |          | 2.2.3 Buck-boost inverting converters       | 52        |

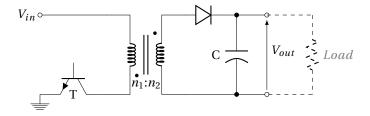

|    |          | 2.2.4 Flyback converters                    | 53        |

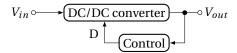

|    | 2.3      | Control                                     | 54        |

|    |          | 2.3.1 Feedback regulation                   | 54        |

|    |          |                                             | 54        |

| Tu | toria    |                                             | 56        |

|    |          |                                             | 57        |

|    | 2.5      |                                             | 57        |

|    | 2.6      |                                             | 58        |

|    | 2.0      |                                             | 58        |

|    |          |                                             | 59        |

|    |          | <u>r</u>                                    | 59        |

|    |          |                                             |           |

|    |          |                                             | 60        |

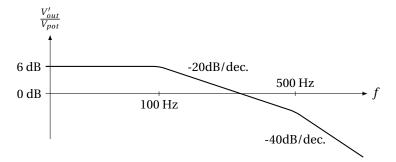

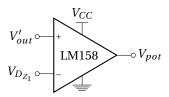

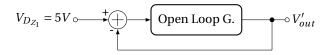

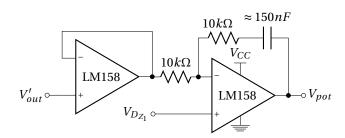

|    |          | 2.6.5 Voltage regulation                    | 60        |

| La | b        |                                             | 63        |

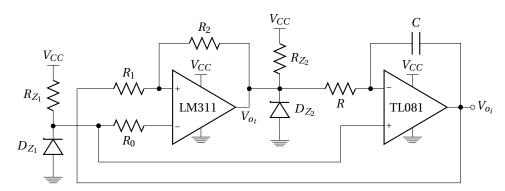

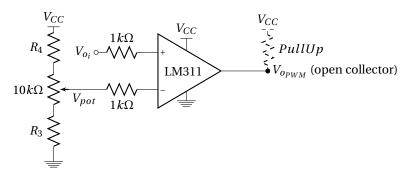

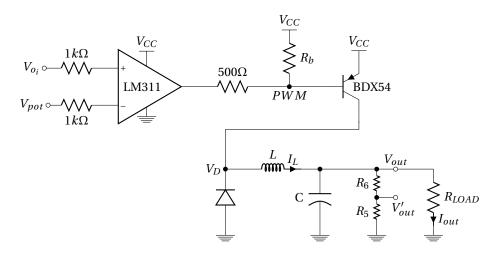

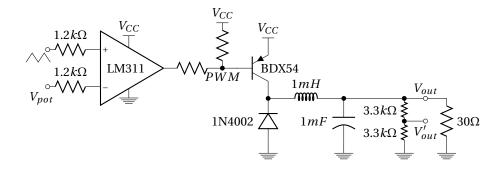

|    | 2.7      | Pulse Width Modulation (PWM)                | 63        |

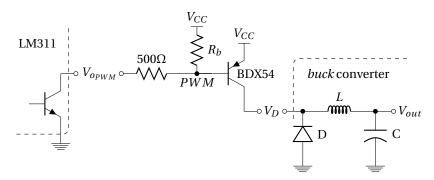

|    | 2.8      | Transistor driver                           | 64        |

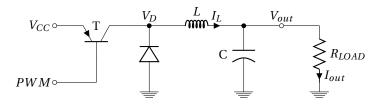

|    | 2.9      | Waveform signals in a <i>buck</i> converter | 64        |

|    |          |                                             | 65        |

|    |          |                                             |           |

| II | <b>P</b> | ase Locked Loop                             | 67        |

| 3  | Pha      | e Locked Loop                               | 69        |

|    | 3.1      | Introduction                                | 69        |

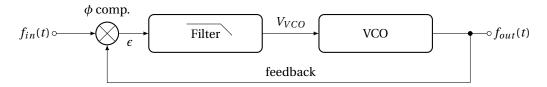

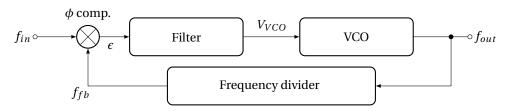

|    | 3.2      | Description                                 | 69        |

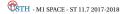

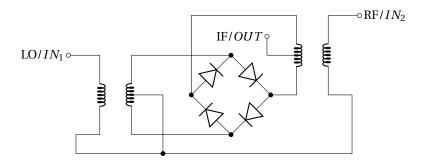

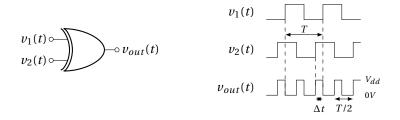

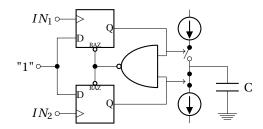

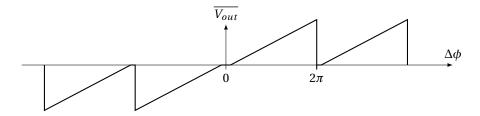

|    |          | 3.2.1 Phase detector/comparator             | 70        |

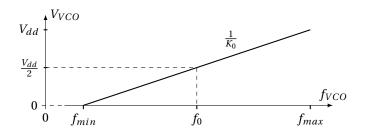

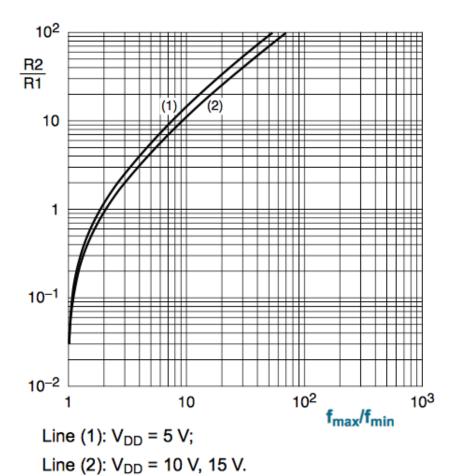

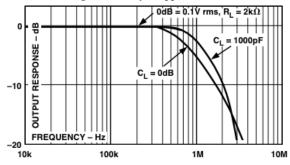

|    |          | 3.2.2 Voltage Control Oscillator - VCO      | 73        |

|    | 3.3      |                                             | 74        |

|    |          |                                             | 74        |

|    |          |                                             | 75        |

|    | 3.4      |                                             | 76        |

|    |          |                                             | 77        |

|    |          |                                             | 77        |

| _  |          |                                             |           |

| Tu | toria    |                                             | <b>79</b> |

|    | 3.5      | 1 2 3 5 .                                   | 79        |

|    |          | o o                                         | 80        |

|    |          | 1                                           | 80        |

|    | 3.6      | 1 7 1                                       | 81        |

|    |          | 1                                           | 81        |

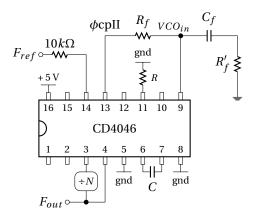

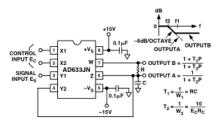

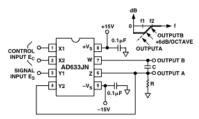

|    |          | 3.6.2 Loop with multiplication              | 82        |

|    |          | 3.6.3 Frequency synthesizes                 | 83        |

| La | ıb         |                                                                        | 84       |

|----|------------|------------------------------------------------------------------------|----------|

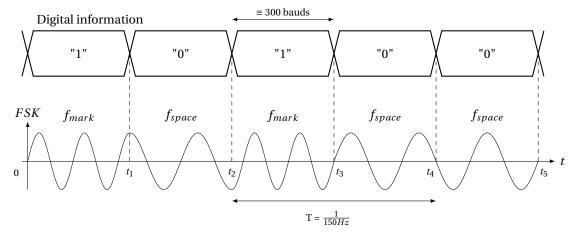

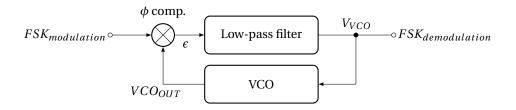

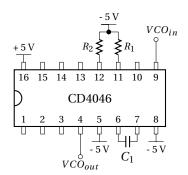

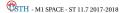

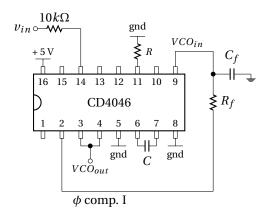

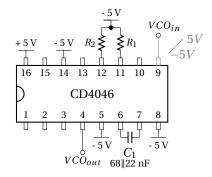

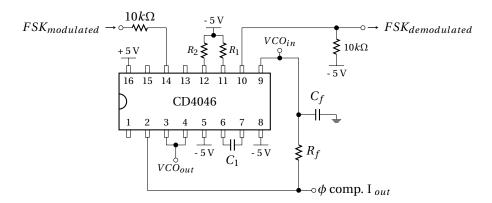

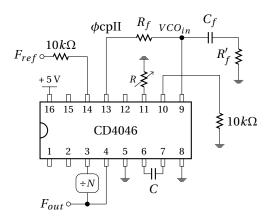

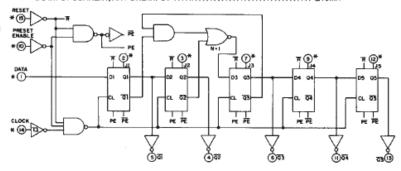

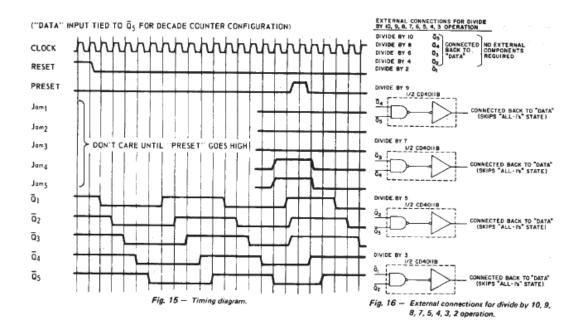

|    | 3.7        | Frequency Shift Keying (FSK) demodulation                              | 85       |

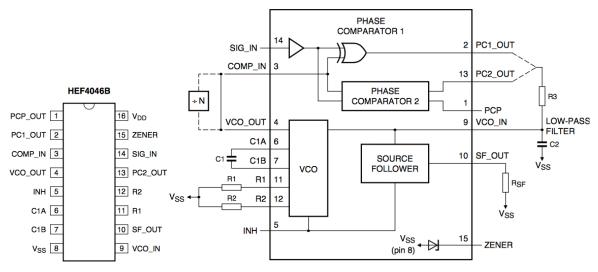

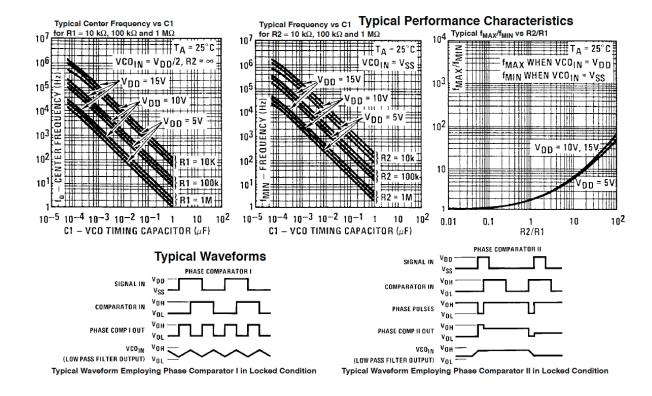

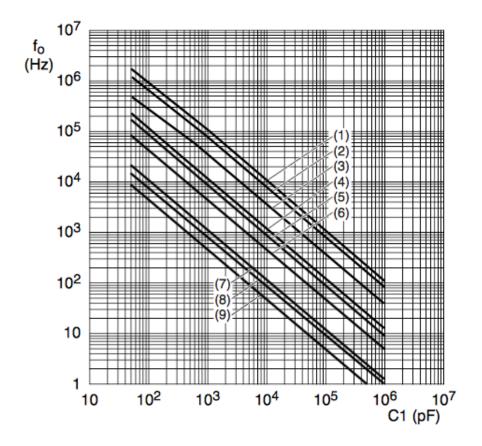

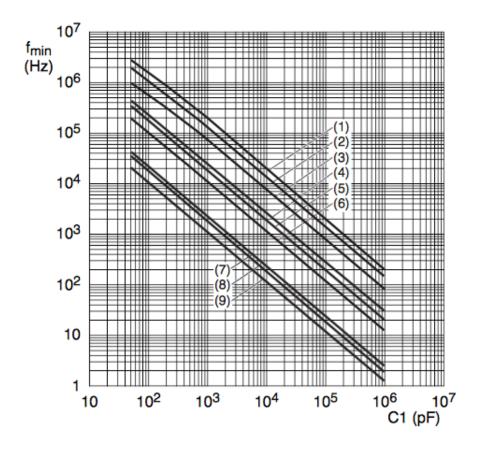

|    |            | 3.7.1 FSK demodulation using a CD4046 PLL                              | 85       |

|    |            | 3.7.2 Frequency Shift Keying (FSK) signal using the function generator | 86       |

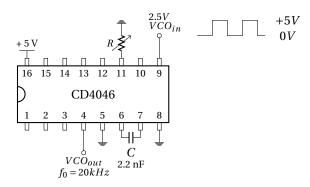

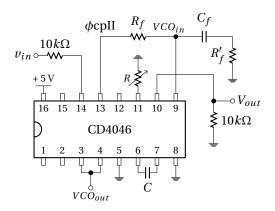

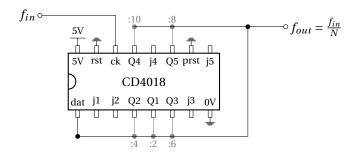

|    | 3.8        | Frequency multiplier                                                   | 87       |

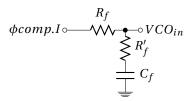

|    |            | 3.8.1 PLL with one pole - one zero loop filter                         | 87       |

|    |            | 3.8.2 Loop with multiplication                                         | 87<br>88 |

|    |            | 3.8.3 Frequency synthesizes                                            | 00       |

| I  | / <b>M</b> | <b>lodulation</b>                                                      | 91       |

| 4  | Mod        | dulation                                                               | 93       |

|    | 4.1        | Introduction                                                           | 93       |

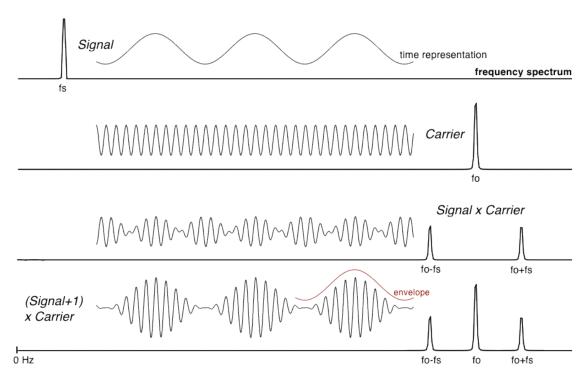

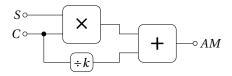

|    | 4.2        | Amplitude modulation                                                   | 94       |

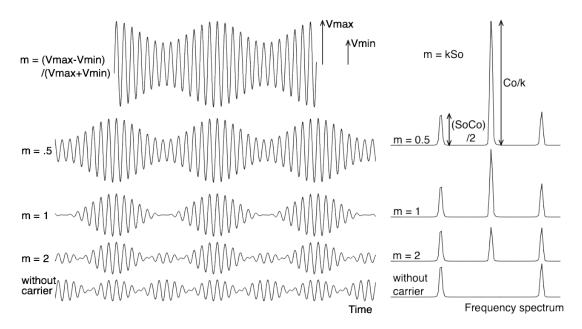

|    |            | 4.2.1 Modulation index                                                 | 96       |

|    | 4.3        | r                                                                      | 97       |

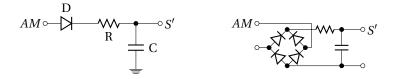

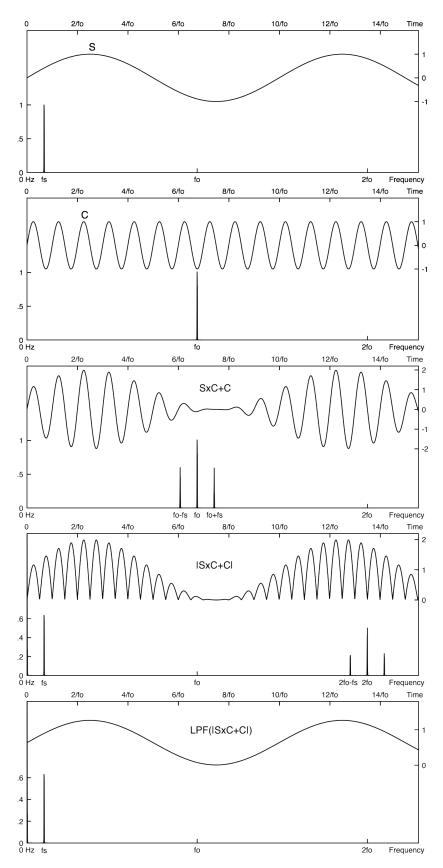

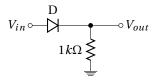

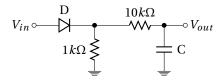

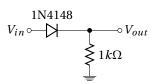

|    |            | 4.3.1 Envelope demodulation                                            | 97       |

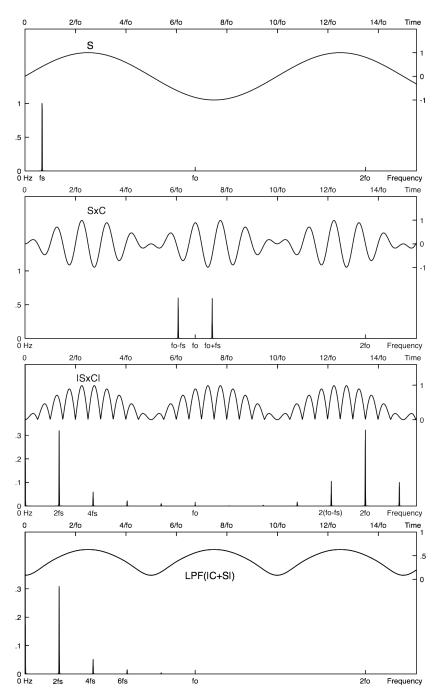

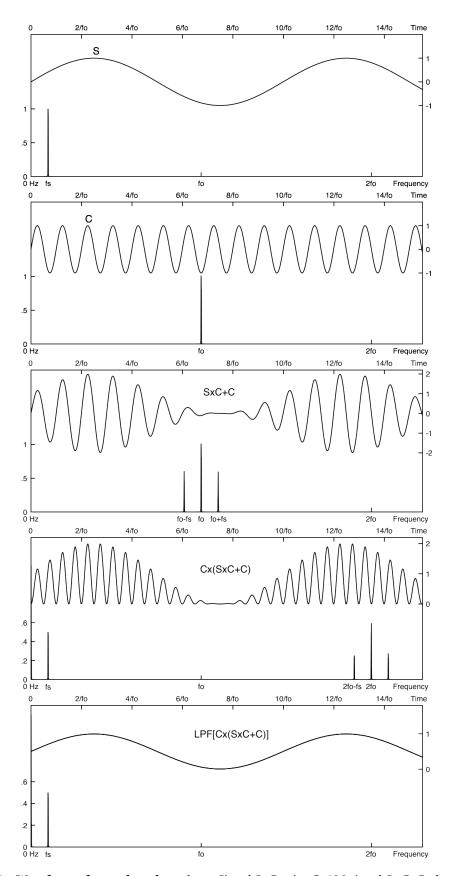

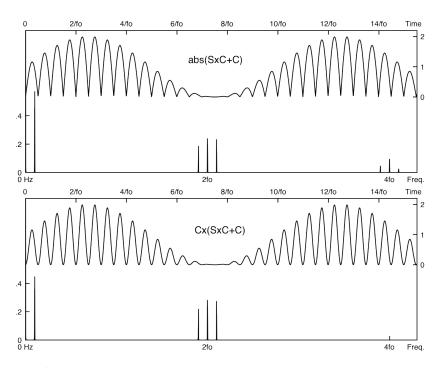

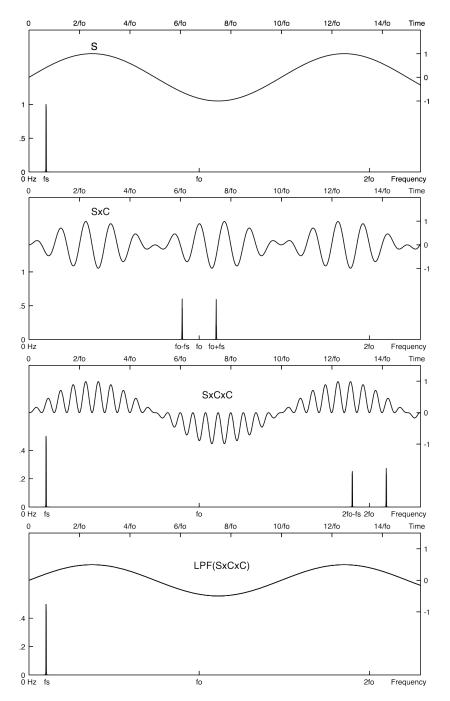

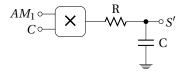

|    |            | 4.3.2 Product demodulation                                             | 99       |

| Tu | ıtoria     | al                                                                     | 105      |

|    | 4.4        | Double Side Bande Amplitude Modulation                                 |          |

|    |            | 4.4.1 Modulation without carrier transmission                          | 105      |

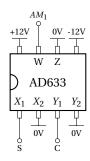

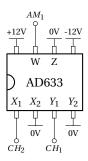

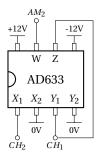

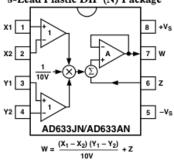

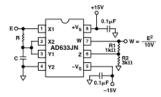

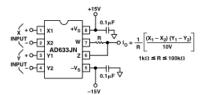

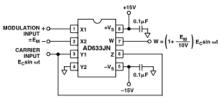

|    |            | 4.4.2 The use of an AD633 as multiplier                                | 106      |

|    |            | 4.4.3 Product detection                                                | 106      |

|    |            | 4.4.4 Modulation with carrier transmission using an AD633              |          |

|    |            | 4.4.5 Modulation index adjustment                                      |          |

|    |            | 4.4.6 Enveloppe detection                                              | 107      |

| La | ıb         |                                                                        | 109      |

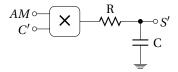

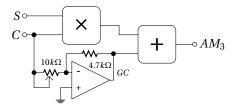

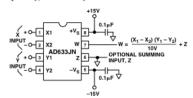

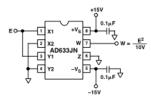

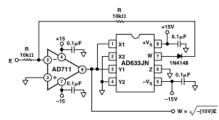

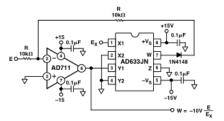

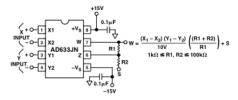

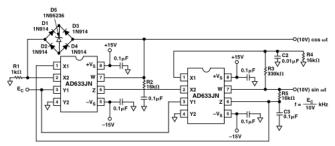

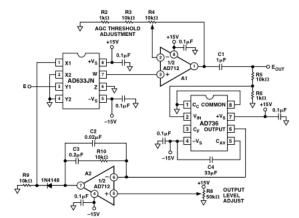

|    | 4.5        | Amplitude modulation as a simple multiplication                        |          |

|    |            | 4.5.1 Modulation                                                       |          |

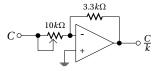

|    |            | 4.5.2 Product detection                                                | 110      |

|    |            | 4.5.3 Modulation with adding carrier                                   | 110      |

|    |            | 4.5.4 Envelope detection                                               | 111      |

| A  | Poly       | ynomials filter tables                                                 | 113      |

| В  | Free       | quency response of polynomial filters                                  | 115      |

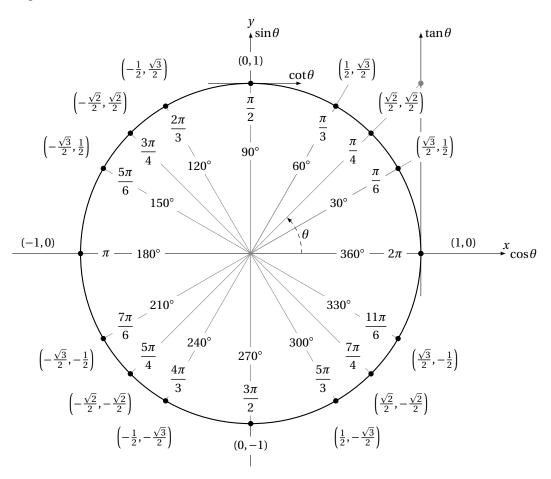

| C  | Ang        | gles, sin and cos transformation formulas                              | 121      |

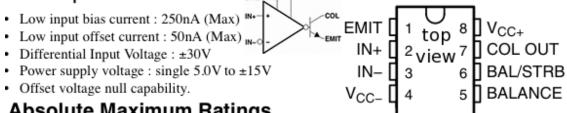

| D  | TL0        | 981 Data Sheet                                                         | 123      |

| E  | LM         | 311 Data Sheet                                                         | 125      |

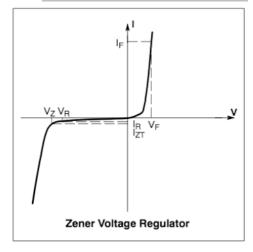

| F  | Zen        | ner diodes Data Sheet                                                  | 127      |

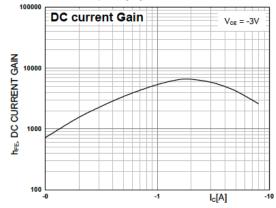

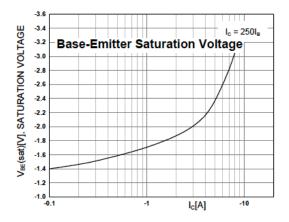

| G  | BDX        | X54 Data Sheet                                                         | 129      |

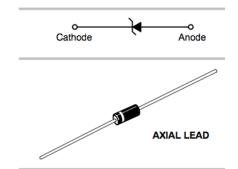

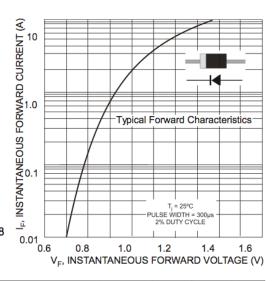

| Н  | Rec        | tifier Data Sheet                                                      | 131      |

| I  | LM         | 158 Data Sheet                                                         | 133      |

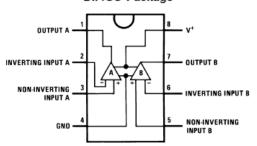

| J  | CD4        | 4046 Data Sheet                                                        | 135      |

| K  | CD4        | 4018 Data Sheet                                                        | 141      |

| L  | ADA        | 633 Data Sheet                                                         | 143      |

| M Signal diode Data Sheet                  | 149 |

|--------------------------------------------|-----|

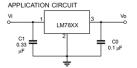

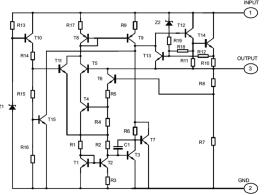

| N 78XX Linear voltage regulator Data Sheet | 151 |

| _ |    |   | ın  |    |  |

|---|----|---|-----|----|--|

| n | re | W | V O | 14 |  |

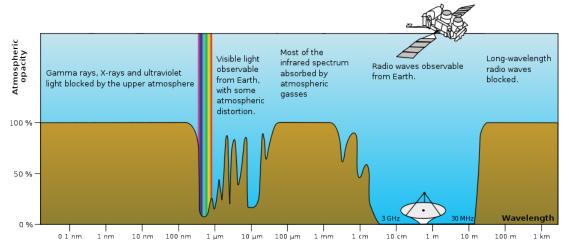

The present document is based on four lectures given for Master of Space and Aeronautics in University of Science and Technology of Hanoi. It consists of four parts. The first one is devoted to **filters**, while the second one deals with **DC/DC converter**, the third one discusses the **phase locked loop** and the last the **modulation**. For convenience of the readers the work is organized so that each part is self-contained and can be read independently. These four electronic systems are chosen because they are representative of critical elements encountered in spacecraft; wether for power supply or for data transmission.

**Acknowledgements:** Damien Prêle was teaching assistants in Paris-6 University for 4 years with professor Michel REDON. Topics of this lecture are inspired from M. Redon's lectures given at Paris-6 University for electronic masters. Therefore, this lecture is dedicated to the memory of professor Michel REDON who gave to the author his understanding of the electronic and helped him to start teaching it.

Moreover, the author would like to express his gratitude to Miss Nguyen Phuong Mai and Mr. Pham Ngoc Dong for their help for the preparation of this teaching in the University of Science and Technology of Hanoi.

Part I

**Filters**

#### **Filters**

#### 1.1 Introduction

A filter performs a **frequency-dependent signal processing**. A filter is generally used to select a useful frequency band out from a wide band signal (example: to isolate station in radio receiver). It is also used to remove unwanted parasitic frequency band (example: rejection of the 50-60 Hz line frequency or DC blocking). Analogue to digital converter also require anti-aliasing low-pass filters.

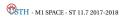

The most common filters are low-pass, high-pass, band-pass and band-stop (or notch if the rejection band is narrow) filters :

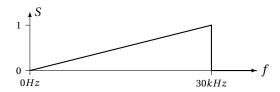

Figure 1.1: Transfer function of ideal filter: Fixed gain in the pass band and zero gain everywhere else; transition at the cutoff frequency.

To do an electronic filter, **devices which have frequency-dependent electric parameter as L and C impedances** are required. The use of these reactive impedances\* into a voltage bridge is the most common method to do a filtering; this is called passive filtering. **Passive (R,L,C) filter is used at high frequencies** due to the low L and C values required. But, **at frequency lower than 1 MHz, it is more common to use active filters made by an operational amplifier** in addition to R and C with reasonable values. Furthermore, active filter parameters are less affected<sup>†</sup> by load impedances than passive one.

## 1.2 Filter parameters

#### 1.2.1 Voltage transfer function

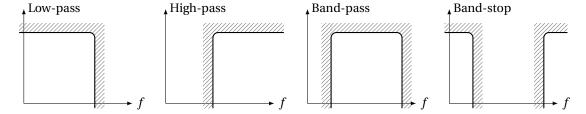

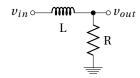

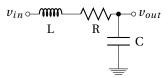

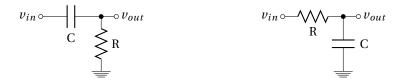

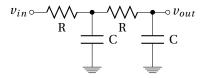

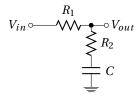

**Passive low-pass filter example:** a first order low-pass filter is made by R-C or L-R circuit as a voltage divider with frequency-dependent impedance. Capacitor impedance  $(Z_C = \frac{1}{jC\omega})$  decreases at high frequency<sup>‡</sup> while inductor impedance  $(Z_L = jL\omega)$  increases. Capacitor is then put across output voltage

$<sup>^*\</sup>mbox{\sc A}$  reactive impedance is a purely imaginary impedance.

$<sup>^\</sup>dagger$ Active filter allows to separate the filter parameters with those matching impedance.

<sup>&</sup>lt;sup>‡</sup>angular frequency  $\omega = 2\pi f$

1. FILTER PARAMETERS 1. FILTERS

and inductor between input and output voltage (Fig. 1.2) to perform low pass filtering.

Figure 1.2: Passive low-pass filter: first order R-C, first order L-R and second order L-C.

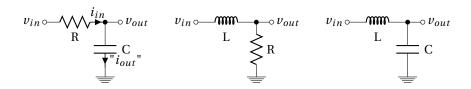

**Generalization:** whatever impedances  $Z_x$  of the voltage bridge shown in figure 1.3, voltage transfer functions H are generalized as expression 1.1 by calculating the divider's voltage ratio using Kirchhoff's voltage law\*.

Figure 1.3: Impedance bridge voltage divider.

$$H(\omega) = \frac{v_{out}}{v_{in}} = \frac{Z_2}{Z_1 + Z_2}$$

(1.1)

Voltage transfer functions of filters given in figure 1.2 are then expressed as:

$$H_{RC} = \frac{Z_C}{R + Z_C} = \frac{\frac{1}{jC\omega}}{R + \frac{1}{jC\omega}} \qquad \Longrightarrow \qquad \boxed{H_{RC} = \frac{1}{1 + jRC\omega}} \tag{1.2}$$

cut-off frequency  $\equiv |H_{RC}| = \frac{1}{\sqrt{2}} \rightarrow RC\omega_c = 1 \rightarrow f_c \Big|_{RC} = \frac{1}{2\pi RC}$

$$H_{LR} = \frac{R}{R + Z_L} = \frac{R}{R + jL\omega} \qquad \Longrightarrow \qquad \boxed{H_{LR} = \frac{1}{1 + j\frac{L}{R}\omega}}$$

$$f_c \Big|_{LR} = \frac{R}{2\pi L}$$

(1.3)

$$H_{LC} = \frac{Z_C}{Z_L + Z_C} = \frac{\frac{1}{jC\omega}}{jL\omega + \frac{1}{jC\omega}} \qquad \Longrightarrow \qquad H_{LC} = \frac{1}{1 - LC\omega^2}$$

(1.4)

$$f_0\Big|_{LC} = \frac{1}{2\pi\sqrt{LC}}$$

A filter can also be used to **convert** a current to a voltage or a voltage to a current in addition to a simple filtering †. Considering for example the first R-C low-pass filter in figure 1.2. We can define

<sup>\*</sup>The sum of the voltage sources in a closed loop is equivalent to the sum of the potential drops in that loop:  $v_{in} = Z_1 \times \frac{v_{out}}{Z_2} + v_{out}$

<sup>&</sup>lt;sup>†</sup>To filter a current, two impedances in parallel are require: current divider. In our example without load impedance  $i_{in} = i_{out}$ . Current transfer function  $\frac{"i_{out}"}{i_{in}}$  is then always equal to 1.

trans-impedance transfer function  $\frac{v_{out}}{i_{in}}$  and also the trans-admittance transfer function  $\frac{"i_{out}"}{v_{in}}$ :

$$\frac{v_{out}}{i_{in}} = \frac{v_{out}}{"i_{out}"} = Z_C = \frac{1}{jC\omega}$$

— Integrator (1.5)

$$\frac{v_{out}}{i_{in}} = \frac{v_{out}}{"i_{out}"} = Z_C = \frac{1}{jC\omega} \longrightarrow \text{Integrator}$$

$$\frac{"i_{out}"}{v_{in}} = \frac{1}{R + Z_C} = \frac{1}{R + \frac{1}{jC\omega}} = \frac{jC\omega}{1 + jRC\omega} \longrightarrow \text{High-pass filter}$$

$$(1.5)$$

#### 1.2.2 S plane (Laplace domain)

For transient analysis, filter transfer function H must be represented as a function of the complex number s:

$$s = \sigma + j\omega \tag{1.7}$$

Then, reactive impedances are expressed as function of this complex number:

$$Z_L = Ls (1.8)$$

$$Z_C = \frac{1}{Cs} \tag{1.9}$$

Frequency response and stability information can be revealed by plotting in a complex plane (s plane) roots values of H(s) numerator (zero) and denominator (pole).

- **Poles** are values of s such that transfer function  $|H| \to \infty$ ,

- **Zeros** are values of *s* such that transfer function |H| = 0.

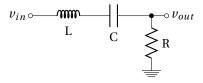

Considering the band-pass filter of the figure 1.4, the transfer function  $H_{LCR} = \frac{v_{out}}{v_{in}}$  is given by equation 1.10.

Figure 1.4: Passive band-pass LCR filter.

$$H_{LCR}(s) = \frac{R}{R + Ls + \frac{1}{Cs}} = \boxed{\frac{RCs}{1 + RCs + LCs^2}}$$

(1.10)

The order of the filter (Fig. 1.4) is given by the degree of the denominator of the expression 1.10. A zero corresponds the numerator equal to zero. A pole is given by the denominator equal to zero. Each pole provides a -20dB/decade slope of the transfer function; each zero a + 20 dB/decade \*. Zero and pole can be real or complex. When they are complex, they have a conjugate pair †.

Expression 1.10 is characterized by a zero at s = 0 and two conjugate poles obtained by nulling it's denominator (eq. 1.11)<sup>‡</sup>.

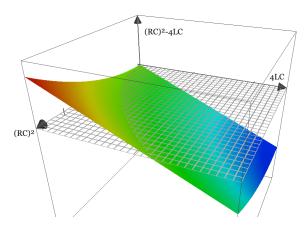

$$0 = 1 + RCs + LCs^2 \xrightarrow{discri.} \Delta = (RC)^2 - 4LC \xrightarrow{roots} s_p = \frac{-RC \pm \sqrt{(RC)^2 - 4LC}}{2LC}$$

(1.11)

The discriminant  $\Delta$  could be positive, null or negative as shown in figure 1.5. The boundary ( $\Delta = 0$ ) between negative and positive discriminant is given by the equation  $(RC)^2 = 4LC$  and could be rewrite  $\frac{1}{2} = \frac{\sqrt{LIC}}{R}$  which is the expression of a parameter called the quality factor Q.

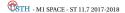

TH - M1 SPACE - ST 11.7 2017-2018

$<sup>*</sup>H[dB] = 20 \log H[lin.]$  and a decade correspond to a variation by a factor of 10 in frequency. A times 10 ordinate increasing on a decade (times 10 abscissa increasing) correspond to a 20dB/decade slope on a logarithmic scale or also 6dB/octave. A -20dB/decade then correspond to a transfer function decreasing by a factor of 10 on a decade

$<sup>^\</sup>dagger each$  conjugate pair has the same real part, but imaginary parts equal in magnitude and opposite in sign

<sup>&</sup>lt;sup>‡</sup>The roots (zeros) of a polynomial of degree 2 (quadratic function)  $ax^2 + bx + c = 0$  are  $x = \frac{-b \pm \sqrt{\Delta}}{2a}$  where the discriminant is  $\Delta = b^2 - 4ac$

Figure 1.5: Discriminant  $\Delta = (RC)^2 - 4LC$  value as function of  $(RC)^2$  and 4LC.

Nature (real or imaginary) of the roots is reported in the table 1.1.

| $\Delta = (RC)^2 - 4LC$ | roots s <sub>p</sub> | $Q = \frac{\sqrt{L/C}}{R}$ |

|-------------------------|----------------------|----------------------------|

| > 0                     | 2 real               | < 1/2                      |

| = 0                     | 1 real <i>double</i> | = 1/2                      |

| < 0                     | 2 complex conjugates | > 1/2                      |

Table 1.1: Link between discriminant sign and nature of the roots. Conditions on the R, L and C device values are reported expressed as the quality factor Q.

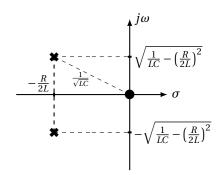

Roots are expressed as two complex conjugate roots  $^*$ : the poles  $s_{p_1}$  and  $s_{p_2}$  given on 1.12.

$$s_{p_{1,2}} = \frac{-R}{2L} \pm j\sqrt{\frac{1}{LC} - \left(\frac{R}{2L}\right)^2}$$

(1.12)

The natural angular frequency  $\omega_0$  is the module of the pole :

$$\omega_0 = |s_{p_{1,2}}| = \frac{1}{\sqrt{LC}} \tag{1.13}$$

In a s plane, pole and zero allow to locate where the magnitude of the transfer function is large (near pole), and where it is small (near zero). This provides us understanding of what the filter does at different frequencies and is used to study the stability. Figure 1.6 shows pole ( $\clubsuit$ ) and zero ( $\bullet$ ) in a s plane.

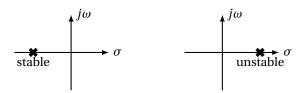

A causal linear system is stable if real part of all poles is negative. On the s plane, this corresponds to a pole localization at the left side (Fig. 1.7).

Laplace notation  $s = \sigma + j\omega$  is required to study stability condition and transient (time domain) analysis. However, for steady state signal (frequency domain) analysis, Fourier notation  $s = j\omega$  is preferred to do harmonic analysis.

#### 1.2.3 Bode plot (Fourier domain)

The most common way to represent the transfer function of a filter is the Bode plot. Bode plot is usually a combination of the magnitude |H| and the phase  $\phi$  of the transfer function on a log frequency axis.

$$\sqrt[*]{x}|_{x<0} = i\sqrt{|x|}$$

Figure 1.6: Pole (★) and zero (◆) representation of the RLC filter (Fig. 1.4) into the *s* plane.

Figure 1.7: Stable if all poles are in the left hand *s* plane (*i.e.* have negative real parts).

Using the LCR band-pass filter (figure 1.4 example), the magnitude\* and the phase<sup>†</sup> of the expression 1.10 (rewrite with unity numerator in 1.14) are respectively given by expressions 1.15 and 1.16. To do this, Fourier transform is used (harmonic regime) instead of Laplace transform: **s is replaced by j** $\omega$ , only.

$$H_{LCR} = \frac{jRC\omega}{1 + jRC\omega - LC\omega^2} = \frac{1}{1 + j\left(\frac{L\omega}{R} - \frac{1}{RC\omega}\right)}$$

(1.14)

$$|H_{LCR}| = \frac{1}{\sqrt{1 + \left(\frac{L\omega}{R} - \frac{1}{RC\omega}\right)^2}}$$

(1.15)

$$\phi_{LCR} = \arg(H_{LCR}) = -\arctan\left(\frac{L\omega}{R} - \frac{1}{RC\omega}\right)$$

(1.16)

**Numerical Application :** L = 1 mH, C = 100 nF and R = 100  $\Omega$

• The natural  $^{\ddagger}$  frequency  $f_0 = \frac{1}{2\pi\sqrt{LC}} = \frac{10^5}{2\pi} \approx 16~kHz$

The band-pass filter could be seen as a cascading high and a low-pass filter:

- The high pass-filter cutoff frequency  $f_{c1} = \frac{R}{2\pi L}$

- The low pass-filter cutoff frequency  $f_{c2} = \frac{1}{2\pi RC}$

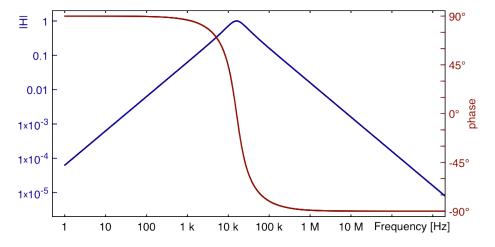

The Bode diagram of this band-pass filter is plotted on figure 1.8.

With this specific numerical application  $f_0 = f_{c1} = f_{c2}$ .  $f_0$ ,  $f_{c1}$  and  $f_{c2}$  are however not necessarily equal. Nevertheless, whatever the numerical application,  $f_0 = \sqrt{f_{c1}f_{c2}}$

**CSTH** - M1 SPACE - ST 11.7 2017-2018

<sup>\*</sup>Absolute value or module

<sup>&</sup>lt;sup>†</sup>Argument

<sup>&</sup>lt;sup>‡</sup>In the case of band-pass filter, *natural frequency* is also called *resonance frequency* or *center frequency* corresponding to  $LC\omega_0^2 = 1$ . This is the frequency at which the impedance of the circuit is purely resistive.

Figure 1.8: Bode plot of the LCR band-pass filter figure 1.4.

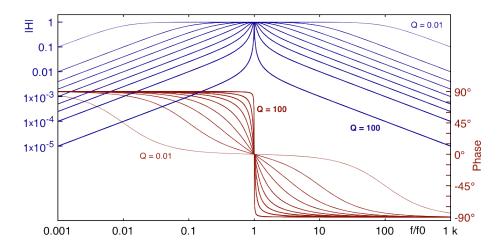

In this numerical application  $f_0=f_{c1}=f_{c2}$  (Fig 1.8). This correspond to a particular case where the quality factor  $Q=\frac{1}{R}\sqrt{\frac{L}{C}}=\frac{1}{100}\sqrt{\frac{10^{-3}}{10^{-7}}}=1$ . For other numerical application (i.e.  $Q\neq 1$ ),  $f_0$  is different than  $f_{c1}$  and  $f_{c2}$  (Fig 1.9).

#### Quality factor Q

Quality factor Q is a dimensionless parameter which indicates how much is the sharpness of a multi-pole filter response around its cut-off (or center \*) frequency. In the case of a band-pass filter, its expression 1.17 is the ratio of the center frequency by the -3 dB bandwidth  $(BW)^{\dagger}$  and is given for series and parallel LCR circuit.

$$Q = \frac{f_0}{BW} = \frac{f_{c2}}{f_{c1}} \Big|_{\text{band-pass filter}}$$

$$= \frac{1}{R} \sqrt{\frac{L}{C}} \Big|_{\text{series LCR}}$$

$$= R \sqrt{\frac{C}{L}} \Big|_{\text{parallel LCR}}$$

(1.17)

Quality factor is directly proportional to the selectivity of a band-pass filter (Fig. 1.9):

- $Q < \frac{1}{2} \rightarrow damped and wide band filter$

- $Q = \frac{1}{2} \rightarrow \text{critically damped}$

- $Q > \frac{1}{2} \rightarrow \text{resonant and narrow band filter}$

We have already see that Q = 1/2 is related to the denominator roots of the transfer function, see table 1.1.

In practice, Q factor is proportional to the ratio between the maximum energy stored in the reactive devices and the energy losses in the resistor :

$$Q = \omega_0 \frac{\text{Max. Energy Stored}}{\text{Power loss}}$$

(1.18)

<sup>†</sup>  $\triangle$  For resonant circuits,  $BW|_{@-3dB} \neq f_{c2} - f_{c1}$ . Indeed, for Q = 1,  $f_{c2} = f_{c1} = f_0$ , but  $BW = f_0$

<sup>\*</sup>for a band-pass filter

The maximum stored energy is  $LI_{L_{RMS}}^2$  or  $CV_{C_{RMS}}^2$ ; the dissipated power is  $RI_{R_{RMS}}^2$  or  $\frac{V_{R_{RMS}}^2}{R}$  and  $\omega_0=2\pi f_0=\frac{1}{\sqrt{LC}}$ . In series LCR,  $I_L=I_C=I_R$ . In parallel LCR,  $V_L=V_C=V_R$ . So, it is easy to link equations 1.17 and 1.18.

We can again rewrite expression 1.14 by using now natural frequency  $f_0$  and quality factor Q:

$$H_{LCR} = \frac{jRC\omega}{1 + jRC\omega - LC\omega^2} = \frac{j\frac{1}{Q}\frac{\omega}{\omega_0}}{1 + j\frac{1}{Q}\frac{\omega}{\omega_0} - \frac{\omega^2}{\omega_0^2}} = \frac{j\frac{1}{Q}\frac{f}{f_0}}{1 + j\frac{1}{Q}\frac{f}{f_0} - \frac{f^2}{f_0^2}} = \frac{1}{1 + jQ\left(\frac{f}{f_0} - \frac{f_0}{f}\right)}$$

(1.19)

with  $RC = \frac{1}{Q} \frac{1}{\omega_0}$ ,  $Q = \frac{1}{R} \sqrt{\frac{L}{C}}$ ,  $\omega_0 = 2\pi f_0 = \frac{1}{\sqrt{LC}}$  and  $\omega = 2\pi f$ .

Figure 1.9: Bode plot of a band-pass filter - Q = 0.01; 0.1; 0.25; 0.5; 1; 2; 4; 10; 100 (*i.e.*  $\zeta = 50$ ; 5; 2; 1; 0.5; 0.25; 0.125; 0.05; 0.005).

#### Damping ratio $\zeta$

Damping ratio  $\zeta$  is generally used in the case of low and hight-pass filter (Low Q) when Q is used in the case of narrow band-pass filter, resonator and oscillator (High Q).

$$\zeta = \frac{1}{2Q} \tag{1.20}$$

The more damping the filter, the flatter its response is and likewise, the less damping the filter, the sharper its response is :

- $\zeta < 1 \rightarrow \text{steep cutoff}$

- $\zeta = 1/\sqrt{2} = Q$   $\rightarrow$  -3dB attenuation at  $f_c$  (as for 1<sup>st</sup> order)

- $\zeta = 1 \rightarrow \text{critical damping}$

- $\zeta > 1 \rightarrow \text{slow cutoff}$

Expression 1.14 may now be rewritten using damping factor:

$$H_{LCR} = \frac{jRC\omega}{1 + jRC\omega - LC\omega^2} = \frac{j2\zeta\frac{\omega}{\omega_0}}{1 + j2\zeta\frac{\omega}{\omega_0} - \frac{\omega^2}{\omega_0^2}}$$

(1.21)

#### 1.3 Cascading filter stages

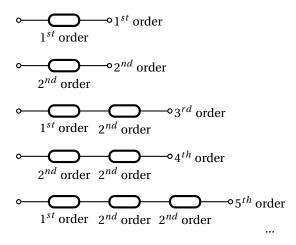

Circuit analysis by applying Kirchhoff's laws (as before) is usually used for first and second order filter. For a higher order filters, network synthesis approach may be used. A polynomial equation expresses the filtering requirement. Each first and second order filter elements are then defined from continued-fraction expansion of the polynomial expression. In practice, to avoid saturation, highest Q stage is placed at the end of the network.

Figure 1.10: Cascading filter stages for higher-order filters.

It exists different type of polynomial equations from which the filter is mathematically derived. These type of filters are Butterworth, Bessel, Chebyshev, inverse Chebyshev, elliptic Cauer, Bessel, optimum Legendre, etc.

- **Butterworth** filter is known as the <u>maximally-flat filter</u> as regards to the flatness in the pass-band. The attenuation is simply -3 dB at the cutoff frequency; above, the slope is -20dB/dec per order (n).

- Chebychev filter has a steeper rolloff\* just after the cutoff frequency but ripple in the pass-band. The cutoff frequency is defined as the frequency at which the response falls below the ripple band †. For a given filter order, a steeper cutoff can be achieved by allowing more ripple in the pass-band (Chebyshev filter transient response shows overshoots).

- **Bessel** filter is characterized by <u>linear phase response</u>. A constant-group delay is obtained at the expense of pass-band flatness and steep rolloff. The attenuation is -3 dB at the cutoff frequency.

- **elliptic Cauer** (non-polynomials) filter has a very fast transition between the pass-band and the stop-band. But it has ripple behavior in both the passband and the stop-band (not studied after).

- **inverse Chebychev Type II** filter is not as steeper rolloff than Chebychev but it has no ripple in the passband but in the stop band (not studied after).

- **optimum Legendre** filter is a tradeoff between moderate rolloff of the Butterworth filter and ripple in the pass-band of the Chebyshev filter. Legendre filter exhibits the maximum possible rolloff consistent with monotonic magnitude response in the pass-band.

<sup>&</sup>lt;sup>†</sup>The cutoff frequency of a Tchebyshev filter is not necessarily defined at - 3dB.  $f_c$  is the frequency value at which the filter transfer function is equal to  $\frac{1}{\sqrt{1+\epsilon^2}}$  but continues to drop into the stop band.  $\epsilon$  is the ripple factor. Chebyshev filter is currently given for a given  $\epsilon$  ( $20\log\sqrt{1+\epsilon}$ ) in [dB].

<sup>\*</sup>rolloff = transition from the pass band to the stop band.

#### 1.3.1 Polynomial equations

Filters are syntheses by using a  $H_0$  DC gain and a polynomial equations  $P_n$ , with n the order of the equation, and so, of the filter. The transfer function of a synthesized low-pass filter is  $H(s) = \frac{H_0}{P_n\left(\frac{s}{\omega_c}\right)}$  with

$\omega_c$  the cutoff angular frequency and  $s = j\omega \Big|_{\text{Fourier domain}} = \sigma + j\omega \Big|_{\text{Laplace domain}}$ .

#### **Butterworth polynomials**

Butterworth polynomials are obtained by using expression 1.22:

$$P_n(\omega) = B_n(\omega) = \sqrt{1 + \left(\frac{\omega}{\omega_c}\right)^{2n}}$$

(1.22)

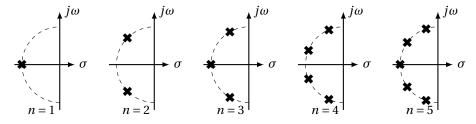

The roots\* of these polynomials occur on a circle of radius  $\omega_c$  at equally spaced points in the s plane:

Figure 1.11: Pole locations of  $1^{st}$ ,  $2^{nd}$ ,  $3^{rd}$ ,  $4^{th}$  and  $5^{th}$  order Butterworth filter.

Poles of a  $H(s)H(-s) = \frac{H_0^2}{1 + \left(\frac{-s^2}{\omega_c^2}\right)^n}$  low pass filter transfer function module are specified by:  $\frac{-s_x^2}{\omega_c^2} = (-1)^{\frac{1}{n}} = e^{j\frac{(2x-1)\pi}{n}} \quad \text{with} \quad x = 1, 2, 3, ..., n$  (1.23)

The denominator of the transfer function may be factorized as

$$H(s) = \frac{H_0}{\prod_{x=1}^{n} \frac{s - s_x}{\omega_c}}$$

(1.24)

The denominator of equation 1.24 is a Butterworth polynomial in s. Butterworth polynomials are usually expressed with real coefficients by multiplying conjugate poles  $^{\dagger}$ . The normalized Butterworth polynomials has the form :

$$B_{0} = 1$$

$$B_{1} = s + 1$$

$$B_{n} = \prod_{x=1}^{\frac{n}{2}} \left[ s^{2} - 2s \cos\left(\frac{2x + n - 1}{2n}\pi\right) + 1 \right] \qquad \text{n is even}$$

$$= (s + 1) \prod_{x=1}^{\frac{n-1}{2}} \left[ s^{2} - 2s \cos\left(\frac{2x + n - 1}{2n}\pi\right) + 1 \right] \qquad \text{n is odd}$$

$$(1.25)$$

Second order Butterworth filter correspond to the particular case where  $Q = \zeta = 1/\sqrt{2} \approx 0.71$ . Indeed, from equation 1.25 and expressing the Butterworth polynomial as the denominator of the equa-

tion 1.19, it is easy to determined for

$$n=2$$

that:  $\frac{1}{Q}=2\cos\left(\frac{2+2-1}{2\times 2}\pi\right)=\sqrt{2}\approx 1.41$  with  $Q=\frac{1}{2\zeta}$  (Eq. 1.20).

\*\*ETH - M1 SPACE - ST 11.7 2017-2018

<sup>\*</sup>Roots of  $B_n$  are poles of the low-pass filter transfer function H(s).

<sup>†</sup>for example  $s_1$  and  $s_n$  are complex conjugates

<sup>&</sup>lt;sup>‡</sup>normalized :  $\omega_c = 1$  and  $H_0 = 1$

#### Chebyshev polynomials

Chebyshev polynomials are obtained by using expression 1.26:

$$P_n = T_n = \begin{cases} \cos(n\arccos(\omega)) & |\omega| \le 1\\ \cosh(n\arccos(\omega)) & |\omega| \ge 1 \end{cases}$$

(1.26)

where the hyperbolic cosine function  $\cosh(x) = \cos(jx) = \frac{e^x + e^{-x}}{2}$ . From the two first values  $T_0 = 1$  and  $T_1 = \omega$ , Chebyshev polynomials  $T_n(\omega)$  could be recursively obtained by using expression 1.27:

$$T_{0} = 1$$

$$T_{1} = \omega$$

$$T_{n} = 2\omega T_{n-1} - T_{n-2} \begin{cases} T_{2} = 2\omega^{2} - 1 \\ T_{3} = 4\omega^{3} - 3\omega \\ T_{4} = 8\omega^{4} - 8\omega^{2} + 1 \\ \dots \end{cases}$$

(1.27)

Chebyshev low-pass filter frequency response is generally obtained by using a slightly more complex expression than for a Butterworth one :

$$|H(s)| = \frac{H_0'}{\sqrt{1 + \epsilon^2 T_n^2 \left(\frac{\omega}{\omega_c}\right)}}$$

(1.28)

where  $\epsilon$  is the ripple factor \*. Even if  $H_0'=1$ , magnitude of a Chebyshev low-pass filter is not necessarily equal to 1 at low frequency ( $\omega=0$ ). Gain will alternate between maxima at 1 and minima at  $\frac{1}{\sqrt{1+\epsilon^2}}$ .

$$T_n\left(\frac{\omega}{\omega_c} = 0\right) = \begin{cases} \pm 1 & n \text{ is even} \\ 0 & n \text{ is odd} \end{cases} \Rightarrow H\left(\frac{\omega}{\omega_c} = 0\right) = \begin{cases} \frac{1}{\sqrt{1+\epsilon^2}} & n \text{ is even} \\ 1 & n \text{ is odd} \end{cases}$$

(1.29)

At the cutoff angular frequency  $\omega_c$ , the gain is also equal to  $\frac{1}{\sqrt{1+\epsilon^2}}$  (but  $\forall n$ ) and, as the frequency increases, it drops into the stop band.

$$T_n\left(\frac{\omega}{\omega_c} = 1\right) = \pm 1 \quad \forall n \quad \Rightarrow \quad H\left(\frac{\omega}{\omega_c} = 1\right) = \pm \frac{1}{\sqrt{1 + \epsilon^2}} \quad \forall n$$

(1.30)

Finally, conjugate poles  $s_x$  (equation 1.31  $^{\dagger}$ ) of expression 1.28 are obtained by solving equation  $0 = 1 + \epsilon^2 T_n^2$ :

$$s_x = \sin\left(\frac{2x - 1}{n} \frac{1}{2\pi}\right) \sinh\left(\frac{1}{n} \operatorname{arcsinh} \frac{1}{\epsilon}\right) + j\cos\left(\frac{2x - 1}{n} \frac{1}{2\pi}\right) \cosh\left(\frac{1}{n} \operatorname{arcsinh} \frac{1}{\epsilon}\right)$$

(1.31)

Using poles, transfer function of a Chebyshev low-pass filter is rewritten as equation 1.28:

$$H(s) = \begin{cases} \frac{\frac{1}{\sqrt{1+\epsilon^2}}}{\prod_{x=1}^{n} \frac{s-s_x}{\omega_c}} & n \text{ is even} \\ \frac{1}{\prod_{n=1}^{n} \frac{s-s_x}{\omega_c}} & n \text{ is odd} \end{cases}$$

(1.32)

<sup>&</sup>lt;sup>†</sup>Poles are located on a centered ellipse in s plane; with real axis of length  $\sinh\left(\frac{1}{n}\arcsin \frac{1}{\epsilon}\right)$  and imaginary axis of length  $\cosh\left(\frac{1}{n}\arcsin \frac{1}{\epsilon}\right)$ .

$<sup>^*\</sup>epsilon$  = 1 for the other polynomials filter and is then not represented

#### Bessel polynomials

Bessel polynomials are obtained by using expression 1.33:

$$P_{n} = \theta_{n} = \sum_{x=0}^{n} s^{x} \frac{(2n-x)!}{2^{n-x}x!(n-x)!} \begin{cases} \theta_{1} = s+1 \\ \theta_{2} = s^{2}+3s+3 \\ \theta_{3} = s^{3}+6s^{2}+15s+15 \\ \dots \end{cases}$$

(1.33)

Bessel low-pass filter frequency response is given by expression 1.34 and is also given for n = 2 (delay normalized second-order Bessel low-pass filter).

$$\frac{\theta_n(0)}{\theta_n\left(\frac{s}{\omega_c}\right)} \quad \Longrightarrow \quad \frac{3}{\left(\frac{s}{\omega_c}\right)^2 + 3\frac{s}{\omega_c} + 3} = \frac{1}{\frac{1}{3}\left(\frac{s}{\omega_c}\right)^2 + \frac{s}{\omega_c} + 1} \tag{1.34}$$

However, Bessel polynomials  $\theta_n$  have been normalized to unit delay at  $\frac{\omega}{\omega_c} = 0$  (delay normalized) and are not directly usable for classical cutoff frequency at -3 dB standard (frequency normalized).

To compare this polynomials to the other one, the table 1.2 gives BCF factors for converting Bessel filter parameters to **3 dB attenuation at**  $\frac{\omega}{\omega_c} = 1$ . These factors were used in preparing the frequency normalized tables given on Appendix I.

| n | BCF    |

|---|--------|

| 2 | 1.3616 |

| 3 | 1.7557 |

| 4 | 2.1139 |

| 5 | 2.4274 |

| 6 | 2.7034 |

| 7 | 2.9517 |

| 8 | 3.1796 |

| 9 | 3.3917 |

Table 1.2: Bessel conversion factor - BCF

By using BCF factor and for n = 2 we finally see in expression 1.35 the frequency response of a second order Bessel low pass filter:

$$H_2 = \frac{1}{\frac{BCF^2}{3} \left(\frac{s}{\omega_c}\right)^2 + BCF\frac{s}{\omega_c} + 1} \approx \frac{1}{0.618 \left(\frac{s}{\omega_c}\right)^2 + 1.3616\frac{s}{\omega_c} + 1}$$

(1.35)

Module and phase are deduced from the equation 1.35:

$$|H_2| = \frac{1}{\sqrt{\left(1 - 0.618 \frac{\omega^2}{\omega_c^2}\right)^2 + \left(1.3616 \frac{\omega}{\omega_c}\right)^2}}$$

$$\phi = \arg(H_2) = -\arctan\left(\frac{1.3616 \frac{\omega}{\omega_c}}{1 - 0.618 \frac{\omega^2}{\omega^2}}\right)$$

(1.36)

Bessel filter is characterized by a linear phase response. Group delay could be studied by calculating:

$$\tau_g = -\frac{d\phi}{d\omega} \tag{1.37}$$

#### Legendre polynomials

From the two first values  $P_0(x) = 1$  and  $P_1(x) = x$ , (as for Chebyshev) Legendre polynomials  $P_n(\omega^2)$  could be recursively obtained by using expression 1.38:

$$P_{0}(x) = 1$$

$$P_{1}(x) = x$$

$$P_{n+1}(x) = \frac{(2n+1)xP_{n}(x) - nP_{n-1}(x)}{n+1} \begin{cases} P_{2}(x) &= \frac{3x^{2}}{2} - \frac{1}{2} \\ P_{3}(x) &= \frac{5x^{3}}{2} - \frac{3x}{2} \\ P_{4}(x) &= \frac{35x^{4}}{8} - \frac{30x^{2}}{8} + \frac{3}{8} \\ \dots \end{cases}$$

$$(1.38)$$

From these polynomials, Legendre low-pass filter (expression 1.39) also called optimal filter are not directly defined from  $P_n$  but from optimal polynomials  $L_n(\omega^2)$  described on expressions 1.40.

$$H(\omega) = \frac{1}{\sqrt{1 + L_n(\omega^2)}}$$

$$L_n(\omega^2) = \begin{cases} \int_{-1}^{2\omega^2 - 1} \left(\sum_{i=0}^k a_i P_i(x)\right)^2 dx & n = 2k + 1 \text{ is odd} \\ \int_{-1}^{2\omega^2 - 1} (x + 1) \left(\sum_{i=0}^k a_i P_i(x)\right)^2 dx & n = 2k + 2 \text{ is even} \end{cases}$$

with  $a_i \begin{cases} n \text{ is odd} & \forall k & a_0 = \frac{a_1}{3} = \frac{a_2}{5} = \dots = \frac{a_i}{2i+1} = \frac{1}{\sqrt{2(k+1)}} \\ a_0 = a_2 = a_4 = \dots = a_i = 0 \end{cases}$

$$\begin{cases} a_1 = \frac{a_3}{3} = \frac{a_3}{7} = \frac{a_5}{11} = \dots = \frac{a_i}{2i+1} = \frac{1}{\sqrt{2(k+1)(k+2)}} \\ a_0 = a_2 = a_4 = \dots = a_i = 0 \end{cases}$$

$$\begin{cases} a_0 = \frac{a_2}{5} = \frac{a_4}{9} = \dots = \frac{a_i}{2i+1} = \frac{1}{\sqrt{2(k+1)(k+2)}} \\ a_1 = a_3 = a_5 = \dots = a_{i-1} = 0 \end{cases}$$

$$(1.39)$$

Finally, optimal polynomials could be calculated:

$$L_{0}(\omega^{2}) = 1$$

$$L_{1}(\omega^{2}) = \omega^{2}$$

$$L_{2}(\omega^{2}) = \omega^{4}$$

$$L_{3}(\omega^{2}) = \omega^{2} - 3\omega^{4} + 3\omega^{6}$$

$$L_{4}(\omega^{2}) = 3\omega^{4} - 8\omega^{6} + 6\omega^{8}$$

$$L_{5}(\omega^{2}) = \omega^{2} - 8\omega^{8} + 28\omega^{6} - 40\omega^{8} + 20\omega^{10}$$

...

Factorization of the overall attenuation function\*  $\sqrt{1 + L_n(\omega^2)}$  is given on Appendix I.

However, it is not so important † to know how found Butterworth, Chebyshev, Bessel or Legendre polynomials coefficients; but it is more useful to know how to use them to design efficient filters. This is why it exists a lot of filter tables to simplify circuit design based on the idea of cascading lower order stages to realize higher-order filters.

#### 1.3.2 Filter Tables

Filter tables could give complex roots or normalized polynomials coefficients  $c_0$ ,  $c_1$ , ...,  $c_n$  with  $P_n = c_n s^n + c_{n-1} s^{n-1} + \cdots + c_1 s + c_0$ . However, more currently filter tables show factorized polynomials or directly normalized cutoff frequency (Scaling Factor - SF) and quality factor (Q) of each of stages for the particular filter being designed.

Some tables are now given using a Butterworth low-pass filter example.

<sup>†</sup>for a filter designer point of view

<sup>\*</sup>Attenuation function = denominator of a low pass filter

#### Roots table

Some filter tables give complex roots of polynomials. Table 1.3 shows roots of Butterworth polynomials (they are obtained by using equation 1.25).

| order n | σ       | jω           |

|---------|---------|--------------|

| 1       | -1      | 0            |

| 2       | -0.7071 | $\pm 0.7071$ |

| 3       | -0.5    | $\pm 0.866$  |

|         | -1      | 0            |

| 4       | -0.3827 | ±0.9239      |

|         | -0.9239 | $\pm 0.3827$ |

| 5       | -0.309  | ±0.951       |

|         | -0.809  | $\pm 0.5878$ |

|         | -1      | 0            |

| 6       | -0.2588 | ±0.9659      |

|         | -0.7071 | $\pm 0.7071$ |

|         | -0.9659 | ±0.2588      |

| 7 | -0.2225 | $\pm 0.9749$ |

|---|---------|--------------|

|   | -0.6235 | $\pm 0.7818$ |

|   | -0.901  | ±0.4339      |

|   | -1      | 0            |

| 8 | -0.1951 | ±0.9808      |

|   | -0.5556 | ±0.8315      |

|   | -0.8315 | ±0.5556      |

|   | -0.9808 | ±0.1951      |

| 9 | -0.1736 | ±0.9848      |

|   | -0.5    | ±0.866       |

|   | -0.766  | ±0.6428      |

|   | -0.9397 | ±0.342       |

|   | -1      | 0            |

Table 1.3: Butterworth polynomials complex roots.

This table is also an indication of pole locations (in s plane) of low-pass filter having Butterworth polynomials as a transfer function denominator. Notice that  $\sigma$  is always negative (stability condition).

#### Polynomials coefficients table

An other table, concerning polynomials, shows directly coefficients  $c_x$  of polynomials as shown in table 1.4 for Butterworth polynomials  $P_n = B_n = \sum_{x=0}^n c_x s^x = c_n s^n + c_{n-1} s^{n-1} + \dots + c_1 s + c_0$ .

| n  | $c_0$ | $c_1$ | $c_2$ | $c_3$ | $c_4$ | $c_5$ | $c_6$ | <i>c</i> <sub>7</sub> | $c_8$ | <i>c</i> <sub>9</sub> | $c_{10}$ |

|----|-------|-------|-------|-------|-------|-------|-------|-----------------------|-------|-----------------------|----------|

| 1  | 1     | 1     |       |       |       |       |       |                       |       |                       |          |

| 2  | 1     | 1.41  | 1     |       |       |       |       |                       |       |                       |          |

| 3  | 1     | 2     | 2     | 1     |       |       |       |                       |       |                       |          |

| 4  | 1     | 2.61  | 3.41  | 2.61  | 1     |       |       |                       |       |                       |          |

| 5  | 1     | 3.24  | 5.24  | 5.24  | 3.24  | 1     |       |                       |       |                       |          |

| 6  | 1     | 3.86  | 7.46  | 9.14  | 7.46  | 3.86  | 1     |                       |       |                       |          |

| 7  | 1     | 4.49  | 10.1  | 14.59 | 14.59 | 10.1  | 4.49  | 1                     |       |                       |          |

| 8  | 1     | 5.13  | 13.14 | 21.85 | 25.69 | 21.85 | 13.14 | 5.13                  | 1     |                       |          |

| 9  | 1     | 5.76  | 16.58 | 31.16 | 41.99 | 41.99 | 31.16 | 16.58                 | 5.76  | 1                     |          |

| 10 | 1     | 6.39  | 20.43 | 42.8  | 64.88 | 74.23 | 64.88 | 42.8                  | 20.43 | 6.39                  | 1        |

Table 1.4: Butterworth polynomials coefficients  $c_x$ .  $P_n = B_n = \sum_{x=0}^n c_x s^x = c_n s^n + c_{n-1} s^{n-1} + \dots + c_1 s + c_0$ .

However, polynomials are generally factored in terms of  $1^{st}$  and  $2^{nd}$  order polynomials; particularly to build cascading  $1^{st}$  and  $2^{nd}$  order filters.

#### Factored polynomials table

To cascade  $1^{st}$  and  $2^{nd}$  order filters (filter synthesis), a more useful table gives a **factored representation of polynomials** as the Butterworth quadratic factors in Table 1.5.

TH - M1 SPACE - ST 11.7 2017-2018

| n  | $P_n = B_n$                                                                                     |

|----|-------------------------------------------------------------------------------------------------|

| 1  | s+1                                                                                             |

| 2  | $s^2 + 1.4142s + 1$                                                                             |

| 3  | $(s+1)(s^2+s+1)$                                                                                |

| 4  | $(s^2 + 0.7654s + 1)(s^2 + 1.8478s + 1)$                                                        |

| 5  | $(s+1)(s^2+0.618s+1)(s^2+1.618s+1)$                                                             |

| 6  | $(s^2 + 0.5176s + 1)(s^2 + 1.4142s + 1)(s^2 + 1.9319s + 1)$                                     |

| 7  | $(s+1)(s^2+0.445s+1)(s^2+1.247s+1)(s^2+1.8019s+1)$                                              |

| 8  | $(s^2 + 0.3902s + 1)(s^2 + 1.1111s + 1)(s^2 + 1.6629s + 1)(s^2 + 1.9616s + 1)$                  |

| 9  | $(s+1)(s^2+0.3473s+1)(s^2+s+1)(s^2+1.5321s+1)(s^2+1.8794s+1)$                                   |

| 10 | $(s^2 + 0.3129s + 1)(s^2 + 0.908s + 1)(s^2 + 1.4142s + 1)(s^2 + 1.782s + 1)(s^2 + 1.9754s + 1)$ |

Table 1.5: Butterworth polynomials quadratic factors.

#### Cutoff frequencies and quality factor table

Finally, an other useful table for filter designer is table which gives directly cutoff frequency and quality factor of each  $2^{nd}$  order filter. Table 1.6 gives frequency scaling factor and quality factor of Butterworth low-pass filter. A first order stage is just defined by a normalized cutoff frequency (SF) without quality factor (Q). Scaling factor is the ratio between the cutoff frequency of the considering stage and the cutoff frequency of the overall cascaded filter. So, finally the polynomial is expressed as in equation 1.42.

$$2^{nd}$$

order polynomial form  $\rightarrow P_n = 1 + j\frac{1}{Q}\frac{f}{SFf_c} - \left(\frac{f}{SFf_c}\right)^2$  (1.42)

$\square$  In the particular case of Butterworth filter, the frequency scaling factor (SF) is always equal to one \*.

| order n | 1 <sup>st</sup> stage |        | 2 <sup>nd</sup> stage |        | 3 <sup>rd</sup> stage |        | 4 <sup>th</sup> stage |        | 5 <sup>th</sup> stage |        |

|---------|-----------------------|--------|-----------------------|--------|-----------------------|--------|-----------------------|--------|-----------------------|--------|

|         | SF                    | Q      |

| 1       | 1                     |        |                       |        |                       |        |                       |        |                       |        |

| 2       | 1                     | 0.7071 |                       |        |                       |        |                       |        |                       |        |

| 3       | 1                     | 1      | 1                     |        |                       |        |                       |        |                       |        |

| 4       | 1                     | 0.5412 | 1                     | 1.3065 |                       |        |                       |        |                       |        |

| 5       | 1                     | 0.618  | 1                     | 1.6181 | 1                     |        |                       |        |                       |        |

| 6       | 1                     | 0.5177 | 1                     | 0.7071 | 1                     | 1.9320 |                       |        |                       |        |

| 7       | 1                     | 0.5549 | 1                     | 0.8019 | 1                     | 2.2472 | 1                     |        |                       |        |

| 8       | 1                     | 0.5098 | 1                     | 0.6013 | 1                     | 0.8999 | 1                     | 2.5628 |                       |        |

| 9       | 1                     | 0.5321 | 1                     | 0.6527 | 1                     | 1      | 1                     | 2.8802 | 1                     |        |

| 10      | 1                     | 0.5062 | 1                     | 0.5612 | 1                     | 0.7071 | 1                     | 1.1013 | 1                     | 3.1969 |

Table 1.6: Butterworth normalized cutoff frequency (Scaling Factor - SF) and quality factor (Q) for each stages.

## 1.3.3 The use of filter tables

To build, for example, a **second order Butterworth low-pass filter** we need to do the transfer function  $H(s) = \frac{H_0}{P_n\left(\frac{s}{\omega_c}\right)}$  where  $P_n$  is a second order Butterworth polynomials *i.e.*  $P_n = B_2$ .

<sup>\*</sup>each  $1^{st}$  and  $2^{nd}$  order filter have the same cutoff frequency than the Butterworth cascading filter has at the end. This is not the case for other polynomials filter as Chebyshev for which SF is often different than 1.

Table 1.3 could be used to write  $B_2 = \left(\frac{s}{\omega_c} - r_1\right) \left(\frac{s}{\omega_c} - r_1^*\right)$  with  $r_1$  and  $r_1^*$  the two conjugate roots  $-0.7071 \pm j0.7071$ . The transfer function of the Butterworth low-pass filter could be expressed as equation 1.43.

$$H(s) = \frac{H_0}{B_2 \left(\frac{s}{\omega_c}\right)} = \frac{H_0}{\left(\frac{s}{\omega_c} + 0.7071 - j0.7071\right)\left(\frac{s}{\omega_c} + 0.7071 + j0.7071\right)}$$

(1.43)

The denominator development of the expression 1.43 gives a quadratic form (expression 1.44) which clearly shows Butterworth polynomial coefficients given on table 1.4 and quadratic factors of table 1.5. It is also clear that expression 1.44 is similar to a classical representation of a transfer function with quality factor where SF and Q are finally what we can directly obtain from the table 1.6.

$$H(s) = \frac{H_0}{\left(\frac{s}{\omega_c}\right)^2 + 1.41 \frac{s}{\omega_c} + 1} = \frac{H_0}{1 + j\frac{1}{Q}\frac{f}{SFf_c} - \frac{f^2}{SF^2f_c^2}} \quad \text{with} \quad \begin{cases} SF = 1\\ Q \approx \frac{1}{1.41} \approx 0.7071 \end{cases}$$

(1.44)

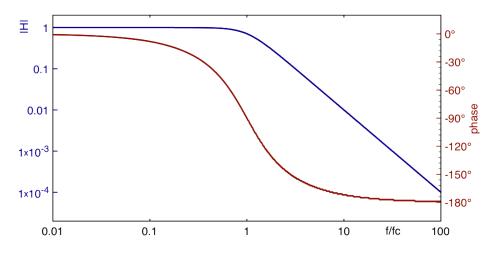

Bode diagram of this low pass filter could be expressed as equation 1.45 and plotted as figure 1.12.

$$|H(\omega)| = \frac{1}{\sqrt{\left[1 - \left(\frac{\omega}{\omega_c}\right)^2\right]^2 + \left(1.41\frac{\omega}{\omega_c}\right)^2}} \quad \text{with} \quad H_0 = 1$$

$$\phi(\omega) = \arg(H) = -\arctan\frac{1.41\frac{\omega}{\omega_c}}{1 - \left(\frac{\omega}{\omega_c}\right)^2}$$

(1.45)

Figure 1.12: Bode plot of a second order Butterworth low-pass filter.

#### 1.3.4 Conversion from low-pass filter

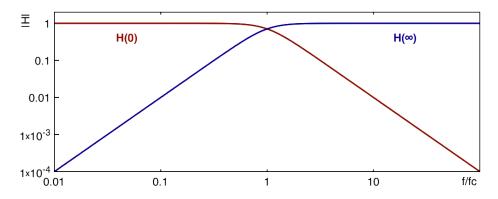

**Low-pass to high-pass filter** Filter tables give polynomials for low and high-pass filter. To obtain a high pass filter, a first order low pass filter transfer function  $\frac{H_0}{c_0+c_1s}$  becomes  $\frac{H_\infty s}{c_1+c_0s}$ ; and a second order low pass filter transfer function  $\frac{H_0}{c_0+c_1s+c_2s^2}$  becomes  $\frac{H_\infty s^2}{c_2+c_1s+c_0s^2}$ . Figure 1.13 shows low and high pass filter with  $H_0$  and  $H_\infty$ \*.

TH - M1 SPACE - ST 11.7 2017-2018

<sup>\*</sup>In practice, there is always a frequency limitation which leads to a low-pass filtering. Consequently, an ideal high-pass filter never exists and  $H_{\infty} \to 0$ . So, in the case of real high pass filter,  $H_{\infty}$  corresponds more to the gain just after the cut-off frequency than that at infinity.

$$H_{LP_1} = \frac{H_0}{c_0 + c_1 s} \qquad \Rightarrow \quad H_{HP_1} = \frac{H_\infty}{c_0 + c_1 / s}$$

$$H_{LP_2} = \frac{H_0}{c_0 + c_1 s + c_2 s^2} \qquad \Rightarrow \quad H_{HP_2} = \frac{H_\infty}{c_0 + c_1 / s + c_2 / s^2}$$

(1.46)

Low to high pass filter conversion:  $s \Rightarrow s^{-1}$

Figure 1.13:  $H_0$  the low frequency gain of a low-pass filter and  $H_\infty$  the high frequency gain of a high-pass filter.

**Band-pass filter** For band-pass filter, it exists specific tables which give specific coefficients given for different bandwidth (BW). However, a low pass filter transfer function could be converted in band-pass filter by replacing s by  $\frac{f_0}{BW} \left( s + s^{-1} \right)$ ; where  $\frac{f_0}{BW}$  is equal to the quality factor Q.

Low to band-pass filter conversion:

$$s \Rightarrow Q(s+s^{-1})$$

**Band-reject filter** A low pass filter transfer function is converted in band-reject filter by replacing *s* by  $\frac{1}{\frac{f_0}{f_0g_2}(s+s^{-1})}$ .

Low to band-reject filter conversion:

$$s \Rightarrow Q^{-1}(s+s^{-1})^{-1}$$

**Transposition** A synthesis of different transpositions are reported in the table 1.7.

| Filter type Conv.               | Low-pass                          | High-pass                         | Band-pass                         | Band-reject                               |

|---------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|-------------------------------------------|

| Normalized complex frequency    | S                                 | $s^{-1}$                          | $Q(s+s^{-1})$                     | $\frac{1}{Q} \frac{1}{s+s^{-1}}$          |

| First order transfert function  | $\frac{1}{C_0 + C_1 s}$           | $\frac{1}{C_0 + C_1/s}$           | $\frac{1}{C_0 + C_1 Q(s+s^{-1})}$ | $\frac{1}{C_0 + \frac{C_1}{Q(s+s^{-1})}}$ |

| Second order transfert function | $\frac{1}{C_0 + C_1 s + C_2 s^2}$ | $\frac{1}{C_0 + C_1/s + C_2/s^2}$ |                                   |                                           |

Table 1.7: Filter normalized transposition.

The transfer function is obtained by using filter table after determination of type and order. The next step is to determine a circuit to implement these filters.

1. FILTERS 1.4. FILTER SYNTHESIS

#### 1.4 Filter synthesis

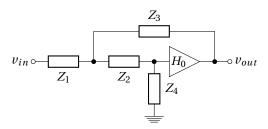

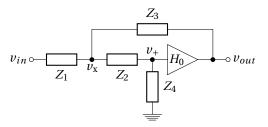

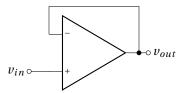

It exists different topologies of filter available for filter synthesis. The most often used topology for an active realization is Sallen-Key topology (Fig. 1.14).

#### 1.4.1 Sallen-Key topology

Sallen-Key electronic circuit (Fig. 1.14) is used to implement second order active filter.

Figure 1.14: Sallen-Key generic topology.

From Kirchhoff laws, transfer function of the generic Sallen-Key topology could be written as:

$$H_{SK} = \frac{H_0}{1 + \left[\frac{Z_1 + Z_2}{Z_4} + (1 - H_0)\frac{Z_1}{Z_3}\right] + \frac{Z_1 Z_2}{Z_3 Z_4}}$$

(1.47)

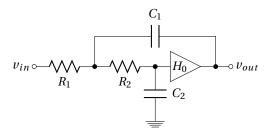

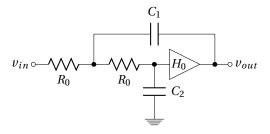

#### Sallen-Key low-pass filter

A low-pass filter is easily obtained from this circuit. Figure 1.15 shows a Sallen-Key low-pass filter.

Figure 1.15: Sallen-Key low-pass filter.

The transfer function of this Sallen-Key low-pass filter is given by equation 1.48.

$$H_{SK_{LP}} = \frac{H_0}{1 + \left[ (R_1 + R_2)C_2 + R_1C_1(1 - H_0) \right] s + R_1R_2C_1C_2s^2}$$

$$= \frac{H_0}{c_0 + c_1s + c_2s^2}$$

$$= \frac{H_0}{1 + j\frac{1}{Q}\frac{f}{SFf_c} - \frac{f^2}{SF^2f_c^2}} \quad \text{with} \quad \begin{cases} SFf_c = \frac{1}{2\pi\sqrt{R_1R_2C_1C_2}} \\ Q = \frac{\sqrt{R_1R_2C_1C_2}}{(R_1 + R_2)C_2 + R_1C_1(1 - H_0)} \end{cases}$$

$$(1.48)$$

This second order Sallen-Key filter can be used to realize one complex-pole pair in the transfer function of a low-pass cascading filter. Values of the Sallen-Key circuit could be chosen to correspond to a polynomials coefficients (as Butterworth, Chebyshev or Bessel...).

1.4. FILTER SYNTHESIS 1. FILTERS

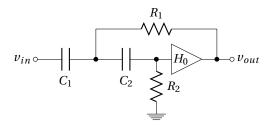

#### Sallen-Key high-pass filter

To transform a low-pass filter to a high-pass filter, all resistors are replaced by capacitors and capacitors by resistors :

Figure 1.16: Sallen-Key high-pass filter.

The transfer function of this Sallen-Key high-pass filter is given by equation 1.49.

$$\begin{split} H_{SK_{HP}} &= H_0 \frac{R_1 R_2 C_1 C_2 s^2}{1 + \left[ R_1 (C_1 + C_2) + R_2 C_2 (1 - H_0) \right] s + R_1 R_2 C_1 C_2 s^2} \\ &= \frac{H_0}{c_0 + \frac{c_1}{s} + \frac{c_2}{s^2}} = \frac{H_0 \frac{c_2}{c_0} s^2}{c_0 + \frac{c_1 c_2}{c_0} s + c_2 s^2} \\ &= \frac{H_0 \frac{-f^2}{SF^2 f_c^2}}{1 + j \frac{1}{Q} \frac{f}{SF f_c} - \frac{f^2}{SF^2 f_c^2}} \quad \text{with} \quad \begin{cases} SF f_c = \frac{1}{2\pi \sqrt{R_1 R_2 C_1 C_2}} \\ Q = \frac{\sqrt{R_1 R_2 C_1 C_2}}{R_1 (C_1 + C_2) + R_2 C_2 (1 - H_0)} \end{cases} \end{split}$$

#### Sallen-Key band-pass filter

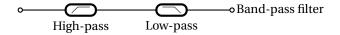

Band-pass filter could be obtained by placing in series a hight and a low pass filter as illustrated in figure 1.17. Cut-off frequency of the low-pass filter need to be higher than the high-pass one; unless you want to make a resonant filter.

Figure 1.17: Cascading high and low-pass filter for band-pass filtering.

A possible arrangement of generic Sallen-Key topology in band-pass configuration is given in figure 1.18.

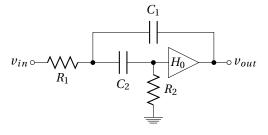

Figure 1.18: Sallen-Key band-pass filter.

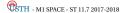

But we can also found more complicated band-pass filter as figure 1.19 based on voltage-controlled voltage-source (VCVS) filter topology which gives the transfer function expressed in equation 1.50.

1. FILTERS 1.4. FILTER SYNTHESIS

Figure 1.19: Voltage-controlled voltage-source (VCVS) filter topology band-pass filter.

$$H_{VCVS_{BP}} = H_0 \frac{\frac{R_2 R_3 C_2}{R_1 + R_3} s}{1 + \frac{R_1 R_3 (C_1 + C_2) + R_2 R_3 C_2 + R_1 R_2 C_2 (1 - H_0)}{R_1 + R_3}} s + \frac{R_1 R_2 R_3 C_1 C_2}{R_1 + R_3} s^2$$

$$= \frac{H'_0 s}{c_0 + c_1 s + c_2 s^2} \quad \text{with} \quad H'_0 = H_0 \frac{R_2 R_3 C_2}{R_1 + R_3}$$

$$= \frac{H'_0 s}{1 + j \frac{1}{Q} \frac{f}{SF f_c} - \frac{f^2}{SF^2 f_c^2}} \quad \text{with} \quad \begin{cases} SF f_c = \frac{1}{2\pi} \sqrt{\frac{R_1 + R_3}{R_1 R_2 R_3 C_1 C_2}} \\ Q = \frac{\sqrt{(R_1 + R_3) R_1 R_2 R_3 C_1 C_2}}{R_1 R_3 (C_1 + C_2) + R_2 R_3 C_2 - R_1 R_2 C_2 (1 - H_0)} \end{cases}$$

$$(1.50)$$

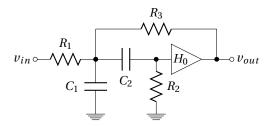

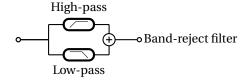

#### Sallen-Key band-reject filter

Unlike the band-pass filter, a notch filter can not be obtained by a series connection of low and high-pass filters. But a summation of the output \* of a low and a high-pass filter could be a band-reject filter if cut-off frequency of the low-pass filter is lower than the high-pass one. This correspond to paralleling high and low-pass filter.

Band-reject filter could be obtained by placing in parallel a high and a low-pass filter as illustrated in figure 1.20.

Figure 1.20: Paralleling low and high-pass filter for band-reject filtering.

A band-reject filter is usualy obtained by using circuit of figure 1.21. Parameters of this simplified Sallen-Key band reject filter is given by expression 1.51.

$$SFf_c = \frac{1}{2\pi\sqrt{RC}}$$

$$Q = \frac{1}{4 - 2H_0}$$

(1.51)

<sup>\*</sup>In practice it is not possible to connect together two outputs without precautions.

Figure 1.21: Sallen-Key band-reject filter.

#### **Amplitude responses** 1.5

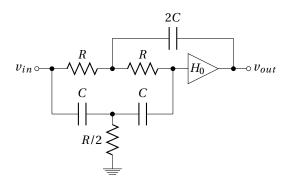

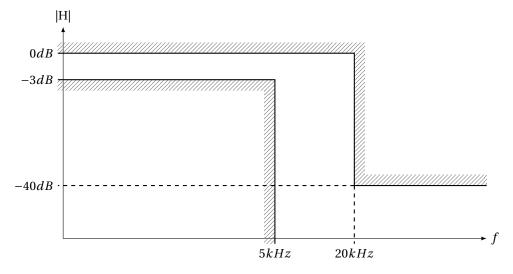

#### Filter specifications 1.5.1

The more common filter specification is the roll-off rate which increases with the order \*. It is 20dB/decade per pole for hight and low-pass filter; per pair of poles/zeros for band-pass filter. Ripples in pass-band and stop-band need to be also specified. Around a cutoff frequency, these specifications could be also defined by 5 transfer function requirements:

- maximum amplitude  $|H|_{max}$

- pass-band cut-off frequency  $f_p^{\ddagger}$

- maximum allowable attenuation in the band-pass  $A_{max}$  §

- frequency at which stop-band begins  $f_s$

- minimum allowable attenuation in the stop-band  $A_{min}$

Figure 1.22 lets appear these various parameters in the case of a low pass filter:

Figure 1.22: Filter amplitude response limits.

<sup>‡</sup> for a -3dB attenuation  $A_{max}$ ,  $f_p$  is the cutoff frequency usually noted  $f_c$ . §  $A_{max} = 3dB$  in the case of Butterworth or Bessel filter and  $A_{max} = \frac{1}{\sqrt{1+\epsilon^2}}$  for Chebyshev filter.

28

<sup>\*</sup>The order of the filter is linked to the number of elements (first and second order filter) used in the network (Fig. 1.10).

<sup>&</sup>lt;sup>†</sup> in the case of low-pass filter,  $|H|_{max} = H_0$  the DC gain and  $H_{\infty}$  in the case of high-pass filter  $|H|_{max}$ , is generally equal to 1.

#### 1.5.2 Amplitude response curves

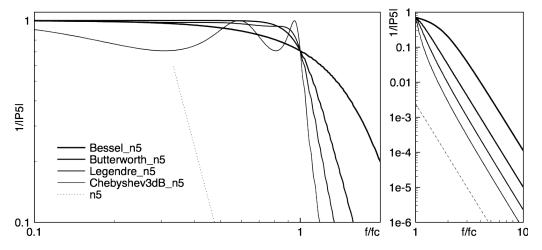

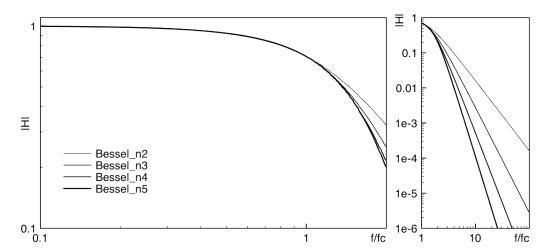

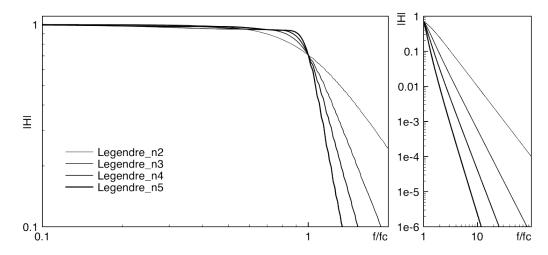

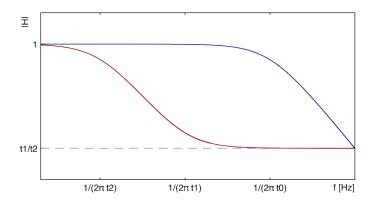

Cebyshev filter has a steeper rolloff near the cutoff frequency when compared to Butterworth and Bessel filters. While, Bessel not exhibit a frequency dependance phase shift as Butterworth and Chebyshev filter. Butterworth is a good compromise as regards to the rolloff, while having a maximaly-flat frequency response. Finally, Legendre filter has the steeper rollof without ripple in the band pass. These kind of comparison between Butterworth, Chebyshev, Bessel and Legendre filter is outlined by figure 1.23, tables 1.8 and 1.9.

Figure 1.23: Steepness and phase linearity filter comparison.

| Properties<br>Filter | Advantages                | Disadvantages             |  |  |

|----------------------|---------------------------|---------------------------|--|--|

| Butterworth          | Maximally flat magnitude  | Overshoot and ringing in  |  |  |

|                      | response in the pass-band | step response             |  |  |

| Chebyshev            | Better attenuation beyond | Ripple in pass-band. Even |  |  |

|                      | the pass-band             | more ringing in step      |  |  |

|                      |                           | response                  |  |  |

| Bessel               | Excellent step response   | Even poorer attenuation   |  |  |

|                      |                           | beyond the pass-band      |  |  |

| Legendre             | Better rolloff without    | pass-band not so flat     |  |  |

|                      | ripple in pass-band       |                           |  |  |

Table 1.8: Butterworth, Chebyshev, Bessel and Legendre filter advantages/disadvantages.

| Filter<br>Properties | Butterworth | Chebyshev            | Bessel    | Legendre |

|----------------------|-------------|----------------------|-----------|----------|

| roll-off rate for a  | average     | good                 | weak      | average  |

| given order          |             |                      |           |          |

| group delay          | good        | bad <b>excellent</b> |           | average  |

| flatness of the      | excellent   | ripple in the        | excellent | good     |

| frequency response   |             | pass-band            |           |          |

| transient response   | good        | average              | excellent | good     |

Table 1.9: Butterworth, Chebyshev, Bessel and Legendre filter comparison.

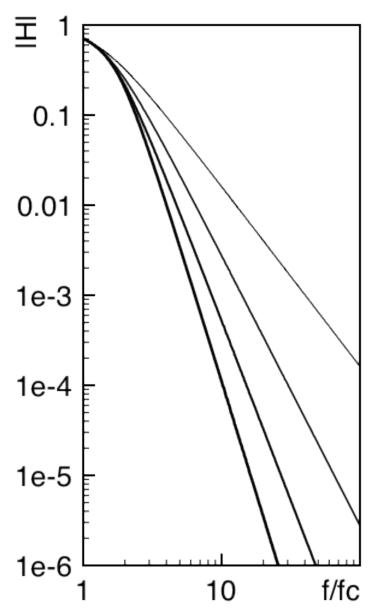

The response of Butterworth, Chebyshev, Bessel and Legendre low-pass filter is compared. To do this, polynomial tables given in Appendix A are directly used as the low-pass filter **denominator** transfer function. Figure 1.24 shows for example the  $5^{th}$  order of Butterworth, Chebyshev, Bessel and Legendre polynomials as a denominator; only the module (expression 1.52) is plotted.

$$P_{5_{\text{Butterworth}}} = (s+1)(s^2+0.618s+1)(s^2+1.618s+1)$$

$$P_{5_{\text{Chebyshev}_{3dB}}} = (5.6328s+1)(2.6525s^2+0.7619s+1)(1.0683s^2+0.1172s+1)$$

$$P_{5_{\text{Bessel}}} = (0.665s+1)(0.3245s^2+0.6215s+1)(0.4128s^2+1.1401s+1)$$

$$P_{5_{\text{Legendre}}} = (2.136s+1)(1.0406s^2+0.3196s+1)(2.0115s^2+1.5614s+1)$$

$$|P_{5}| = \begin{cases} \sqrt{\left(\frac{f^2}{f_c^2}+1\right)\left(\left(\frac{f^2}{f_c^2}+1\right)^2+0.618^2\frac{f^2}{f_c^2}\right)\left(\left(\frac{f^2}{f_c^2}+1\right)^2+1.618^2\frac{f^2}{f_c^2}\right)} \\ \sqrt{\left(5.6328^2\frac{f^2}{f_c^2}+1\right)\left(\left(2.6525\frac{f^2}{f_c^2}+1\right)^2+0.7619^2\frac{f^2}{f_c^2}\right)\left(\left(1.0683\frac{f^2}{f_c^2}+1\right)^2+0.1172^2\frac{f^2}{f_c^2}\right)} \\ \sqrt{\left(0.665^2\frac{f^2}{f_c^2}+1\right)\left(\left(0.3245\frac{f^2}{f_c^2}+1\right)^2+0.6215^2\frac{f^2}{f_c^2}\right)\left(\left(0.4128\frac{f^2}{f_c^2}+1\right)^2+1.1401^2\frac{f^2}{f_c^2}\right)}} \\ \sqrt{\left(2.136^2\frac{f^2}{f_c^2}+1\right)\left(\left(1.0406\frac{f^2}{f_c^2}+1\right)^2+0.3196^2\frac{f^2}{f_c^2}\right)\left(\left(2.0115\frac{f^2}{f_c^2}+1\right)^2+1.5614^2\frac{f^2}{f_c^2}\right)}} \end{cases}$$

It clearly appears on figure 1.24 differences, concerning frequency response, between Butterworth, Chebyshev, Bessel and Legendre filters. All these filters have been plotted with a cutoff frequency referred to a -3dB attenuation. Thereby, despite the same order, Chebyshev filter has the faster rolloff, then come Legendre, Butterworth and the slower is the Bessel filter. Far after the cutoff frequency, the slope becomes the same for all  $5^{th}$  order filters ( $\propto f^{-5}$ ) but not the attenuation for a given  $\frac{f}{f_c}$ .

Figure 1.24: Frequency response of a Butterworth, Chebyshev, Bessel and Legendre  $5^{th}$  order low-pass filter around cutoff frequency and far after it. Dashed line represent a  $f^{-5}$  slope for comparison to  $5^{th}$  order filter rolloff.

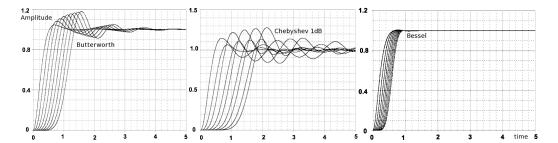

The drawback of a fast rolloff is the increasing of the transit time to step response as shown in figure 1.25. Time response of a Chebyshev filter clearly shows oscillations which increase the settling time\*.

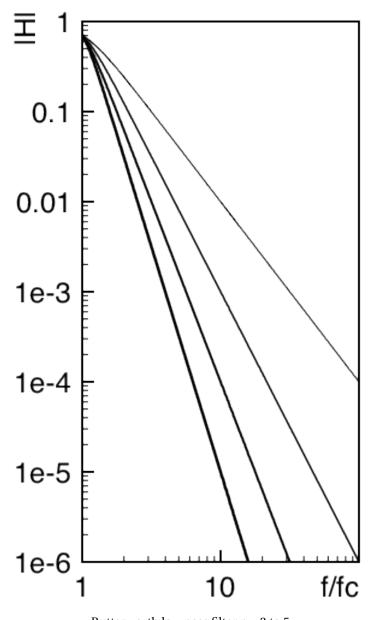

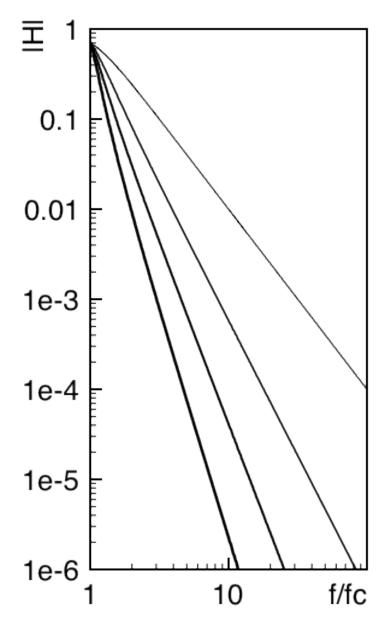

#### **Butterworth frequency response**

Figure 1.26 illustrates the main properties of Butterworth filters which is the flatness in the pass-band; particularly for high order.

Butterworth attenuation plot on the right side of figure 1.26 could be used to determined the needed order for a given  $A_{min}$  and  $f_s$  (Fig. 1.22).

<sup>\*</sup>Settling time is the time requires to reach and stay around the final voltage with a specified errors; usually a range of 1%, 2% or 5%

Figure 1.25: Normalized ( $f_c = 1$ ) time response (step) of multipole (2 to 10) Butterworth, Chebyshev 1dB and Bessel low-pass filters.

Figure 1.26: Frequency response of a Butterworth low-pass filter for n = 2 to 5.

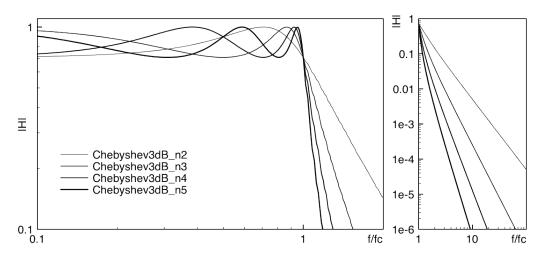

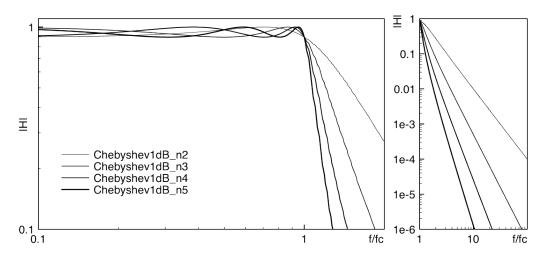

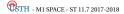

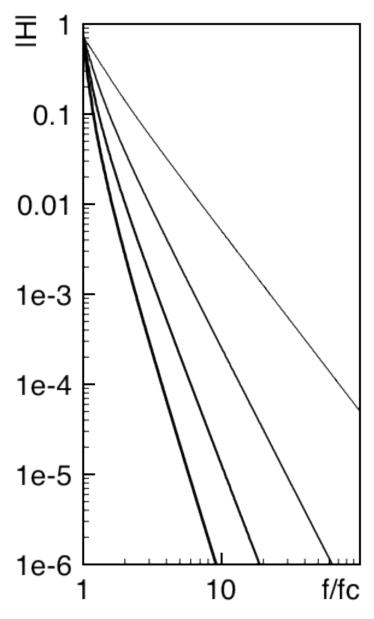

#### Chebyshev frequency response

Figure 1.27 shows the ripple in the pass-band of a Chebyshev low-pass filter (3dB) for order from 2 to 5. It also appears that  $H_0$  (numerator) is different from 1 for **even order**. For an even order Chebyshev filter with a ripple factor of 3 dB (which correspond to  $\epsilon = 1$ ), the numerator is equal to  $\frac{1}{\sqrt{1+\epsilon^2}} \approx 0.71$ .

Figure 1.28 shows more precisely the difference in  $H_0$  between odd (n=5  $\rightarrow$   $H_0$  = 1) and even (n=4  $\rightarrow$   $H_0 \approx 0.707$ ) order. It also illustrates of how it is possible to determine the order of a Chebyshev filter by simply counting the ripple number on the transfer function.

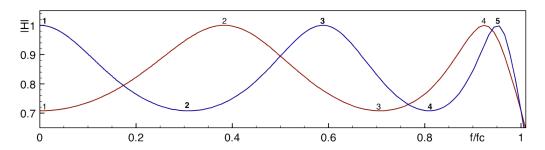

Amplitudes of the ripples in the pass-band is constrained by the  $|H|_{max}-A_{max}$  and  $f_c$  (Fig. 1.22). Sometimes, ripple factor needs to be smaller than 3dB. It is easy to find Chebyshev polynomials table with a ripple factor of 1 dB\*, 0.5 dB or 0.1 dB. In Figure 1.29, is plotted the transfer function of a Chebyshev low-pass filter with a ripple factor of 1 dB ( $\epsilon$  = 0.5) and order going from 2 to 5. The  $H_0$  of even order is set at  $\frac{1}{\sqrt{1+0.5^2}} \approx 0.894$  as it is shown in figure 1.30.

Finally, a comparison between two Chebishev low-pass filters with different ripple factor is plotted in figure 1.31. Even if the cutoff frequency is referred to a different level (-1 dB and -3 dB), it appears that the larger the ripple factor, the faster the rolloff.

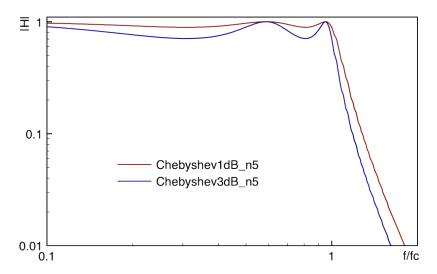

#### Bessel frequency response

Figure 1.32 show Bessel low-pass filter transfer function from the  $2^{nd}$  to the  $5^{th}$  order. The rolloff is much slower than for other filters. Indeed, Bessel filter maximizes the flatness of the group delay curve in the pass-band (Fig. 1.33) but not the rolloff. So, for a same attenuation in the stop-band ( $A_{min}$ ), a higher order is required compared to Butterworth, Chebyshev or Legendre filter.

$<sup>^*</sup>$ Chebyshev polynomials table is given in Appendix A for a ripple factor of 3 and 1 dB

Figure 1.27: Frequency response of a Chebishev ( $\epsilon = 1$ ) low pass filter for n = 2 to 5.

Figure 1.28: Zoom in the passband of the frequency response of a Chebishev ( $\epsilon$  = 1) low-pass filter for n = 4 and 5.

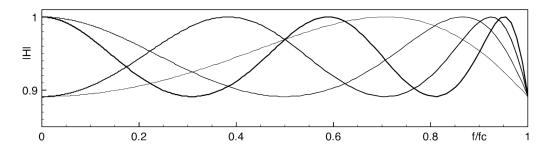

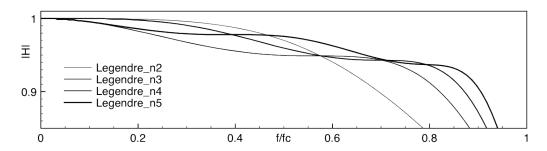

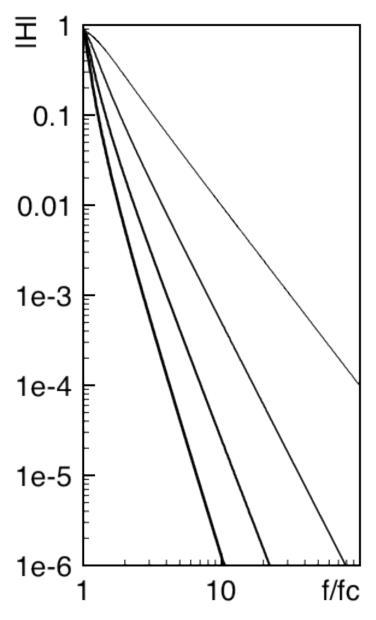

#### Legendre frequency response

To complete this inventory, Legendre low-pass filter frequency response is plotted in figure 1.34 for n = 2 to 5.

Legendre filter is characterized by the maximum possible rolloff consistent with monotonic magnitude response in the pass-band. But monotonic does not flat, as we can see in figure 1.35.

As for Chebyshev filter, it is possible to count the number of "ripples" to find the order from a plotted transfer function.

Figure 1.29: Frequency response of a Chebishev ( $\epsilon = 0.5$ ) low-pass filter for n = 2 to 5 order filter rolloff.

Figure 1.30: Zoom in the pass-band of the frequency response of a Chebishev ( $\epsilon = 0.5$ ) low-pass filter for n = 2 to 5.

## 1.6 Switched capacitor filters

A switched capacitor electronic circuit works by moving charges into and out of capacitors when switches are opened and closed. Filters implemented with these elements are termed "switched-capacitor filters".

#### 1.6.1 Switched capacitor

Figure 1.36 give the circuit of a switched capacitor resistor, made of one capacitor C and two switches  $S_1$  and  $S_2$  which connect the capacitor with a given frequency alternately to  $V_{in}$  and  $V_{out}$ . Each switching cycle transfers a charge from the input to the output at the switching frequency. When  $S_1$  is closed while  $S_2$  is open, the charge stored in the capacitor C is  $q_{in} = CV_{in}^*$ , when  $S_2$  is closed, some of that charge is transferred out of the capacitor, after which the charge that remains in capacitor C is  $q_{out} = CV_{out}$ .

Thus, the charge moved out of the capacitor to the output is  $q_T = q_{in} - q_{out} = C(V_{in} - V_{out})$ . Because this charge  $q_T$  is transferred each  $T_S^{\dagger}$ , the rate of transfer of charge per unit time  $^{\ddagger}$  is given by expression 1.53.

$$I = \frac{q_T}{T_S} = \frac{C(V_{in} - V_{out})}{T_S}$$

(1.53)

Expression 1.53 gives a link between V and I, and then the impedance  $^{\S}$  of the switched capacitor

<sup>§</sup>The impedance of the capacitor could be considered static for a frequency smaller than  $\frac{1}{T_s}$ .

$<sup>\</sup>ensuremath{^*} \mbox{q=CV}, \mbox{q}$  the charge on a capacitor C with a voltage V between the plates.

$<sup>^{\</sup>dagger}T_{S}$  Periodicity of switch opening and closing.

<sup>&</sup>lt;sup>‡</sup>The rate of flow of electric charge is a current I[A].

Figure 1.31: Comparison between frequency response of two Chebishev low-pass filters of  $5^{th}$  order, one with a ripple factor of 1 dB, and the other with 3 dB.

Figure 1.32: Frequency response of a Bessel low-pass filter for n = 2 to 5.

which could be expressed as a resistor (expression 1.54).

$$R = \frac{T_s}{C} \tag{1.54}$$

Switching capacitor behaves like a lossless resistor whose value depends on capacitance C and switching frequency  $\frac{1}{T_S}$ . This reduces energy consumption for embedded applications (such as space mission) and allows an adjustment of the resistance value.

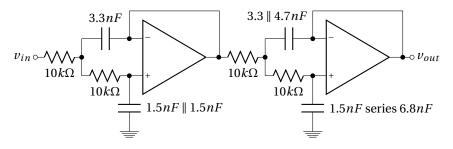

## 1.6.2 Switched capacitor filters

Because switching capacitor act as a resistor, **switched capacitors can be used instead of resistors** in the previous filter circuits (RC, RLC, Sallen-Key ...). A  $R=10k\Omega$  can be replaced by a switched capacitor following the expression 1.54. Using a switching clock  $f_s=\frac{1}{T_S}=50kHz$ , the capacitor is given by equation 1.55.

$$R = 10k\Omega \equiv C = \frac{1}{10k\Omega \times 50kHz} = 2nF$$

(1.55)

Figure 1.33: Comparison of the delay time as a function of frequency  $\left(\frac{f}{f_c}\right)$  between a Bessel, a Butterworth and a Chebyshev low-pass filter (n=4).

Figure 1.34: Frequency response of a Legendre low-pass filter for n = 2 to 5

A variation of the switching frequency leads to a variation of the equivalent resistance R. If  $f_s$  increases,  $R = \frac{1}{C \times f_s}$  decreases. This link between frequency and equivalent resistance value could be used to modify a filter cutoff frequency by adjusting the switching frequency.

The cutoff frequency of a RC switched capacitor filter (Fig. 1.37) is expressed by equation 1.56.

$$f_c = \frac{1}{2\pi R_{equiv.}C_2} = \frac{C_1 \times f_s}{2\pi C_2}$$

(1.56)

If the switching frequency  $f_s$  increases, the cutoff frequency  $f_c$  increases too.

Figure 1.35: Zoom on the pass-band of the frequency response of a Legendre low-pass filter for n = 2 to 5.

$$V_{in} \circ \begin{array}{c} S_1 & S_2 \\ \\ \times & \\ \end{array} = \begin{array}{c} V_{out} & \\ \end{array} = \begin{array}{c} R \\ V_{in} \circ \begin{array}{c} \\ \\ \end{array} \\ \end{array} V_{out}$$

Figure 1.36: Equivalence between Resistor and Switched Capacitor.

$$V_{in} \circ \longrightarrow \bigvee_{\underline{\qquad}} C_2 \qquad \equiv \qquad V_{in} \circ \longrightarrow \bigvee_{\underline{\qquad}} C_1 \qquad \downarrow_{\underline{\qquad}} C_2 \qquad \qquad \downarrow_{\underline{\qquad}} C_2$$

Figure 1.37: Equivalence between RC filter and switched capacitor filter.

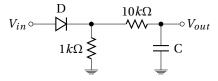

# 1.7 First order passive filter

Transfer function of the first order filter (Fig. 1.38).

Figure 1.38: First order LR filter.

- 1. Give the expression of the  $\frac{v_{out}(\omega)}{v_{in}(\omega)}$  transfer function.

- 2. Is it a low or a high-pass filter?

$$R = 1k\Omega$$

and  $L = 1mH$ :

- 3. What is the cutoff frequency?

- 4. Give the module and the phase of this transfer function as a function of f.

- 5. Draw the Bode plots of the filter.

- 6. Same questions for the two following filters :  $R = 22k\Omega$  and C = 33nF

Figure 1.39: 2 other First order filters.

## 1.8 Second order passive filter

Transfer function of the second order filter (Fig. 1.40).

L = 1mH,  $R = 1\Omega$  and C = 100nF:

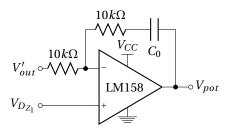

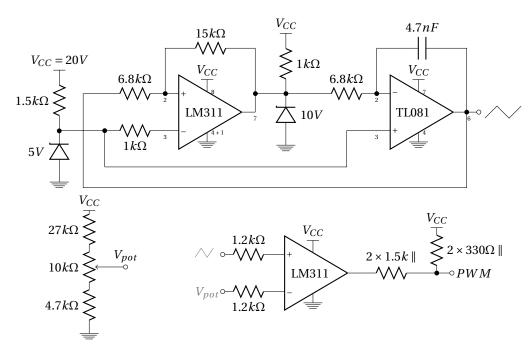

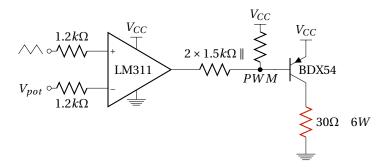

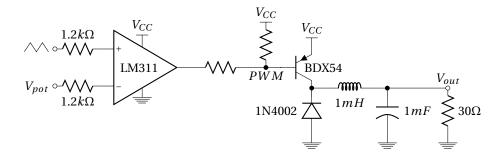

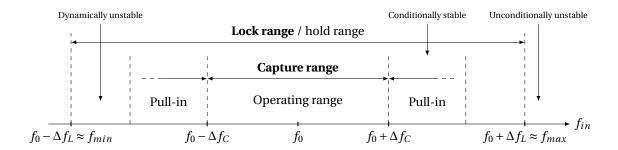

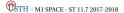

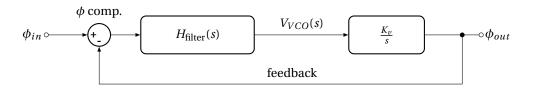

- 1. Give the expression of the  $\frac{v_{out}(\omega)}{v_{in}(\omega)}$  transfer function highlighting the damping factor  $\zeta$ .